## CSCE 351 Operating System Kernels

## **Intel Architecture**

Steve Goddard goddard@cse.unl.edu

http://www.cse.unl.edu/~goddard/Courses/CSCE351

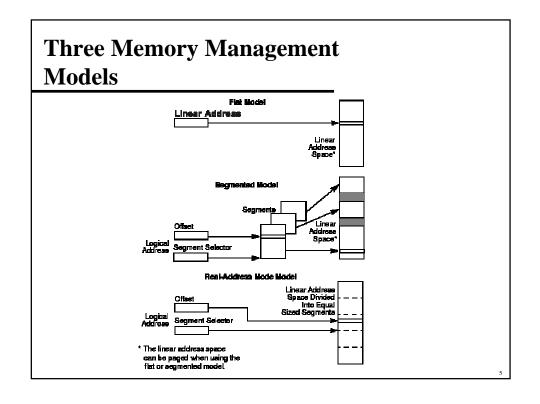

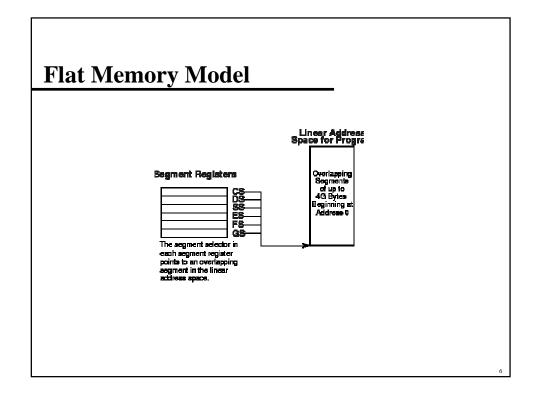

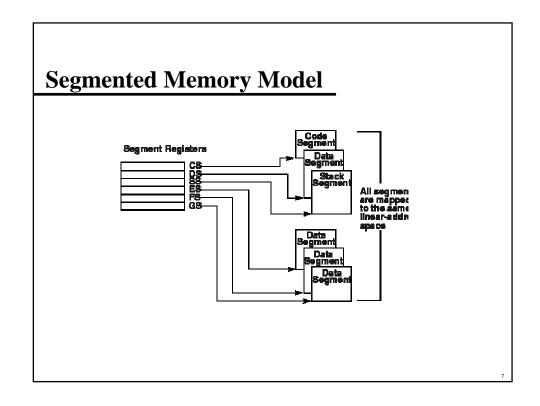

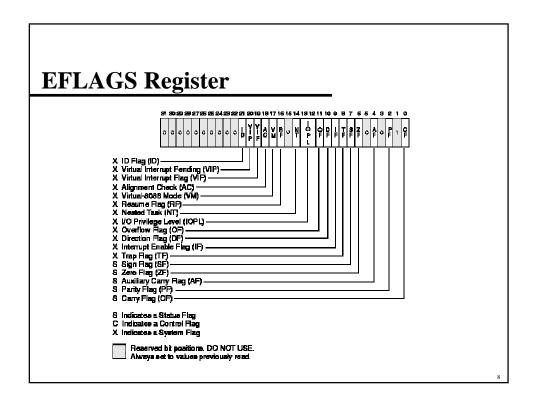

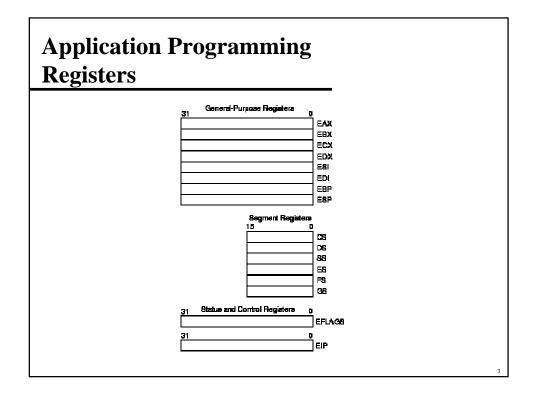

**Basic Execution Environment** 2<sup>ce</sup> -11 Eight 32-bit Registers General-Purpose Registers Six 16-bit Segment Registers Address Registers Space\* 32-bits **EFLAGS Register** 32-bits EIP (Instruction Pointer Register) 'The address space can be flat or segmented.

## Alternate General-Purpose Register Names

| General-Purpose Registers |    |      |    |   |        |        |

|---------------------------|----|------|----|---|--------|--------|

| 31                        | 16 | 15 8 | 7  | 0 | 16-b H | 32-bit |

|                           |    | AH   | AL |   | ΑX     | EAX    |

|                           |    | ВН   | BL |   | BX     | EBX    |

|                           |    | CH   | CL |   | CX     | ECX    |

|                           |    | DH   | DL |   | DX     | EDX    |

|                           |    | BP   |    |   |        | EBP    |

|                           |    | 엶    |    |   |        | ESI    |

|                           |    | DI   |    |   |        | EDI    |

|                           |    | SP   |    |   |        | ESP.   |

4