Coding verilog

Download as ppt, pdf1 like4,132 views

The document provides an overview of using Verilog for designing combinational circuits, outlining key steps such as understanding the problem, simplifying logic, and implementing designs using structural or behavioral styles. It compares Verilog with VHDL, explains simulation and synthesis, and details data types, operators, and the principles of modular design. Additionally, it emphasizes the importance of thinking in hardware rather than traditional programming approaches when writing Verilog code.

1 of 30

Downloaded 35 times

![9

Data types

Values on a wire

0, 1, x (unknown or conflict), z (tristate or

unconnected)

Vectors

A[3:0] vector of 4 bits: A[3], A[2], A[1], A[0]

Unsigned integer value

Indices must be constants](https://image.slidesharecdn.com/07-verilog-160305205040/85/Coding-verilog-9-320.jpg)

![10

Manipulating vectors

Concatenating bits/vectors, use { }

e.g. sign extend

B[7:0] = {A[3], A[3], A[3], A[3], A[3:0]};

B[7:0] = {4{A[3]}, A[3:0]};

Style: Use a[7:0] = b[7:0] + c[7:0]

Not a = b + c;](https://image.slidesharecdn.com/07-verilog-160305205040/85/Coding-verilog-10-320.jpg)

![13

Numbers are unsigned

C[4:0] = A[3:0] + B[3:0];

if A = 0110 (6) and B = 1010(–6),

then C = 10000 (not 00000)

B is zero-padded, not sign-extended](https://image.slidesharecdn.com/07-verilog-160305205040/85/Coding-verilog-13-320.jpg)

![21

Behavioral 4-bit adder

module add4 (SUM, OVER, A, B);

input [3:0] A;

input [3:0] B;

output [3:0] SUM;

output OVER;

assign {OVER, SUM[3:0]} = A[3:0] + B[3:0];

endmodule

“[3:0] A” is a 4-wire bus labeled “A”

Bit 3 is the MSB

Bit 0 is the LSB

Can also write “[0:3] A”

Bit 0 is the MSB

Bit 3 is the LSB

Buses are implicitly connected—

If you write BUS[3:2], BUS[1:0],

they become part of BUS[3:0]](https://image.slidesharecdn.com/07-verilog-160305205040/85/Coding-verilog-21-320.jpg)

![22

Continuous assignment

Assignment is continuously evaluated

Corresponds to a logic gate

Assignments execute in parallel

assign A = X | (Y & ~Z);

assign B[3:0] = 4'b01XX;

assign C[15:0] = 16'h00ff;

assign #3 {Cout, Sum[3:0]} = A[3:0] + B[3:0] + Cin;

gate delay (used by simulator)

Boolean operators

(~ for bit-wise negation)

bits can assume four values

(0, 1, X, Z)

variables can be n-bits wide

(MSB:LSB)](https://image.slidesharecdn.com/07-verilog-160305205040/85/Coding-verilog-22-320.jpg)

![25

4-bit comparator

// Make a 4-bit comparator from 4 1-bit comparators

module Compare4(Equal, Alarger, Blarger, A4, B4);

input [3:0] A4, B4;

output Equal, Alarger, Blarger;

wire e0, e1, e2, e3, Al0, Al1, Al2, Al3, B10, Bl1, Bl2, Bl3;

Compare1 cp0(e0, Al0, Bl0, A4[0], B4[0]);

Compare1 cp1(e1, Al1, Bl1, A4[1], B4[1]);

Compare1 cp2(e2, Al2, Bl2, A4[2], B4[2]);

Compare1 cp3(e3, Al3, Bl3, A4[3], B4[3]);

assign Equal = (e0 & e1 & e2 & e3);

assign Alarger = (Al3 | (Al2 & e3) |

(Al1 & e3 & e2) |

(Al0 & e3 & e2 & e1));

assign Blarger = (~Alarger & ~Equal);

endmodule](https://image.slidesharecdn.com/07-verilog-160305205040/85/Coding-verilog-25-320.jpg)

Ad

Recommended

Verilog VHDL code Decoder and Encoder

Verilog VHDL code Decoder and EncoderBharti Airtel Ltd. This document summarizes an experiment that implemented 2:4, 3:8 decoders and an 8:3 encoder using Verilog. It provides the Verilog code for each implementation and includes RTL simulation output waveforms. The aim was to model the decoders and encoder using dataflow and behavioral modeling. The experiment was conducted using Xilinx ISE 9.2i software by student SHYAMVEER SINGH with roll number B-54.

multiplexers and demultiplexers

multiplexers and demultiplexersUnsa Shakir This document discusses multiplexers and demultiplexers. It defines them as devices that allow digital information from several sources to be routed onto a single line (multiplexers) or distributed to multiple output lines (demultiplexers). The key properties of multiplexers and demultiplexers are described, including the relationship between the number of inputs, outputs, and selection lines. Examples of implementing multiplexers and demultiplexers using logic gates are provided.

Verilog hdl

Verilog hdlMuhammad Uzair Rasheed Hardware description languages (HDLs) allow designers to describe digital systems at different levels of abstraction in a textual format. The two most commonly used HDLs are Verilog and VHDL. Verilog is commonly used in the US, while VHDL is more popular in Europe. HDLs enable simulation of designs before fabrication to verify functionality. Digital designs can be modeled at the gate level, data flow level, or behavioral level in Verilog. Verilog code consists of a design module and test bench module to stimulate inputs and observe outputs.

Verilog VHDL code Parallel adder

Verilog VHDL code Parallel adder Bharti Airtel Ltd. Experiment 5 implements a parallel adder using half adders and full adders. It uses Verilog code to design a 4-bit parallel adder with inputs a and b. The adder uses half adders for the least significant bits and full adders for the remaining bits, storing any carry bits in variables. An RTL simulation verifies the adder design works as intended by summing the parallel binary bits with carry.

Day2 Verilog HDL Basic

Day2 Verilog HDL BasicRon Liu Verilog HDL Basics covers the basics of Verilog including data types, modules, simulation, operators, assignments, and flow control. It discusses key concepts like event-driven simulation, blocking vs non-blocking assignments, continuous assignments, initial and always blocks, and control structures like if, case, for loops. The document provides examples to illustrate Verilog syntax and how it is used to model hardware at the register transfer level.

Modulo n counter

Modulo n counterManoj Guha A modulus-n counter is a sequential logic device that counts through a predetermined sequence of states when triggered by a clock signal. The number of states it cycles through before returning to the initial state is called its modulus. For example, a 2-bit counter with states 00, 01, 10, 11 has a modulus of 4. The maximum modulus of an n-bit counter is 2^n. Modulus counters are used in applications like frequency counters, digital clocks, time measurement, and more.

Multiplexers and Demultiplexers

Multiplexers and DemultiplexersGargiKhanna1 This document discusses multiplexers and demultiplexers. It defines them as digital switches that allow multiple inputs to be selected for a single output (multiplexer), or a single input to be routed to multiple outputs (demultiplexer). It provides examples of their applications and internal workings, including the relationship between the number of select lines and the number of inputs/outputs. Circuit diagrams and truth tables are presented to illustrate 4-to-1 multiplexers and 1-to-4 demultiplexers. Advantages of using multiplexers in logic design are also summarized.

Modules and ports in Verilog HDL

Modules and ports in Verilog HDLanand hd The document discusses modules and ports in Verilog. It describes that a module defines distinct parts including module name, port list, port declarations, and optional parameters. Ports provide the interface for a module to communicate with its environment. There are two methods for connecting ports to external signals - by ordered list where signals must appear in the same order as ports, and by name where the order does not matter as long as port names match. Hierarchical names provide unique names for every identifier by denoting the design hierarchy with identifiers separated by periods.

Verilog Tasks and functions

Verilog Tasks and functionsVinchipsytm Vlsitraining The document outlines the use of tasks and functions in Verilog HDL, emphasizing their purpose in behavioral modeling and code reuse. Functions return a single value without timing control, while tasks can have timing controls and multiple input/output arguments. Key differences and examples of their declaration and invocation are also provided.

VHDL- gate level modelling

VHDL- gate level modellingVandanaPagar1 This document provides an overview of Verilog hardware description language (HDL) and gate-level modeling. It discusses the key components of Verilog modules like module definition, ports, parameters and instantiations. It describes how to define ports and connect ports in a module. It also covers different gate primitives in Verilog like AND, OR, NOT etc. and how to describe gate-level designs using these primitives by specifying gate connections and delays. Finally, it mentions some references for further reading on Verilog HDL and digital logic design.

Interfacing methods of microcontroller

Interfacing methods of microcontrollerDiwaker Pant The document discusses microcontroller interfacing. It defines interfacing as the transfer of data between microcontrollers and peripherals using buses. Interfacing is needed to connect a microcontroller's computation capabilities to external signals or devices to enable man-machine interaction. Various interfacing methods are described, including wiring techniques like wires, buses, and pins. Examples of interfacing a microcontroller to memory and I/O devices are provided. Common microcontroller interfaces like digital input/output, analog, serial interfaces are also summarized along with their applications and advantages/disadvantages.

module1:Introduction to digital electronics

module1:Introduction to digital electronicschandrakant shinde The document provides an overview of the Analog and Digital Electronics course taught at Matoshri College of Engineering & Research Centre. It includes information about the course's teaching scheme, examination scheme, objectives, and outcomes. The objectives are to design logical, sequential and combinational digital circuits using K-maps and to develop concepts related to operational amplifiers and rectifiers. The document also provides details of the topics to be covered in the first unit including Boolean algebra, K-maps, and the design of combinational circuits. It introduces concepts such as logic gates, number systems, and digital signals.

Digital electronics logic families

Digital electronics logic familiesBLESSINAR0 This document provides an overview of different digital logic families. It begins by introducing logic gates and integrated circuits. It then classifies logic families as either bipolar or unipolar, and lists examples of each. Key specifications of digital ICs are defined, including propagation delay, fan-in/fan-out, input/output logic levels, and noise margin. Transistor-transistor logic (TTL) and complementary metal-oxide-semiconductor (CMOS) circuits are described. The TTL NAND gate uses multiple emitter transistors while the CMOS NAND gate uses both P-channel and N-channel MOSFETs. Emitter-coupled logic (ECL) provides the fastest

Magnitude comparator

Magnitude comparatorSyed Saeed - The document discusses magnitude comparators, which are used to compare two binary numbers and output whether the first number is less than, equal to, or greater than the second number.

- It explains 1-bit and 2-bit magnitude comparators, providing their truth tables and logic diagrams. For a 1-bit comparator, it derives the logic expressions for the three outputs using K-maps.

- For a 2-bit comparator, it similarly provides the truth table and derives the K-map expressions for the three outputs. It then shows the full logic diagram for a 2-bit magnitude comparator using AND, OR, and NOT gates.

verilog code for logic gates

verilog code for logic gatesRakesh kumar jha The document contains Verilog code for half adders and full adders. It provides two implementations for each: a half adder is implemented using XOR and AND gates to calculate the sum and carry outputs from two input bits, and a full adder uses additional gates to calculate the sum and carry from three input bits.

Basics of digital verilog design(alok singh kanpur)

Basics of digital verilog design(alok singh kanpur)Alok Singh The document discusses the use of Verilog, a hardware description language (HDL), for digital design, emphasizing its importance as designs grow more complex. It compares Verilog with VHDL, detailing the advantages of its concise syntax and hierarchical modeling capabilities. The document covers various abstraction levels in HDLs, highlighting the transition from gate-level designs to higher-level behavioral models for efficient verification and synthesis.

Verilog Test Bench

Verilog Test BenchDr.YNM The document discusses the process of verifying a chip's design using a Verilog testbench, which is a HDL code that applies input stimuli to the design under test (DUT) and captures its output for comparison with expected results. It outlines the structure and steps for creating a testbench, including initializing inputs, generating test vectors, and checking the DUT's behavior against predefined outputs. The document also provides examples of testbenches for various digital circuits, such as NAND gates, half-adders, and full-adders.

Encoder

EncoderMahmudul Hasan This presentation introduces encoders. It discusses that an encoder is a combinational circuit that performs the reverse operation of a decoder, with a maximum of 2n inputs and n outputs. The simplest encoder is a 2n-to-n binary encoder, where one of the 2n inputs is 1 and the output is an n-bit binary number representing the activated input. An example of an 8-to-3 binary encoder is shown, where only one of the 8 inputs can be activated at a time, and the 3 outputs represent the activated input in binary code.

Complex Programmable Logic Device (CPLD) Architecture and Its Applications

Complex Programmable Logic Device (CPLD) Architecture and Its Applicationselprocus A Complex Programmable Logic Device (CPLD) is an integrated circuit used to implement digital logic, characterized by multiple programmable logic blocks that can handle more complex designs than Simple Programmable Logic Devices (SPLDs) but less than Field Programmable Gate Arrays (FPGAs). CPLDs are ideal for high-performance applications and are often utilized in portable devices due to their low power consumption and small size. They can be programmed using languages like Verilog or VHDL, with the design process involving simulation, synthesis, and a place-and-route stage to fit the architecture.

Multiplexers & Demultiplexers

Multiplexers & DemultiplexersJayanshu Gundaniya Multiplexers and demultiplexers allow digital information from multiple sources to be routed through a single line. A multiplexer has multiple data inputs, select lines to choose an input, and a single output. A demultiplexer has a single input, select lines to choose an output, and multiple outputs. Bigger multiplexers and demultiplexers can be built by cascading smaller ones. Multiplexers can implement logic functions by using the select lines as variables and routing the input lines to the output.

Verilog HDL

Verilog HDLMantra VLSI This document provides an introduction to Verilog HDL including:

- An overview of Verilog keywords, data types, abstraction levels, and design methodology.

- Details on the history of Verilog including its development over time and transitions to newer standards.

- Explanations of key Verilog concepts like modules, ports, instantiation, stimuli, and lexical conventions.

Modules are the basic building blocks, ports define module interfaces, and instantiation replicates modules. Stimuli provide test inputs and lexical conventions cover syntax rules.

Transistor Transistor Logic

Transistor Transistor Logicsurat murthy The document provides an overview of transistor-transistor logic (TTL) and its applications in digital circuits, detailing the evolution and variations of TTL technology since its introduction in 1963. It explains different TTL sub-families, their characteristics such as power dissipation and speed, and comparisons with other logic families like resistor-transistor logic and CMOS. Additionally, it outlines key parameters like propagation delay and speed-power product that are crucial for evaluating TTL performance.

Sequence detector Verilog Code

Sequence detector Verilog CodeBharti Airtel Ltd. This document describes an experiment to implement a sequence detector using behavioral modeling. The sequence detector will output a 1 when it detects the input sequence of 11011. It includes the state transition diagram for detecting the 1011 sequence and the Verilog code for the sequence detector module. The code defines the different states like s0, s1, etc. and uses case statements to transition between the states based on the current input and update the output. The learning outcome is understanding how to detect a sequence step-by-step and learning Xilinx software commands.

boolean algebra and logic simplification

boolean algebra and logic simplificationUnsa Shakir The document provides an overview of Boolean algebra and logic simplification. It covers topics such as Boolean variables that can take true/false or 1/0 values, basic logic gates like AND, OR, NOT, NAND and NOR gates, canonical forms including sum-of-products and product-of-sums, De Morgan's laws, and examples of simplifying Boolean expressions and implementing logic circuits.

Verilog Tutorial - Verilog HDL Tutorial with Examples

Verilog Tutorial - Verilog HDL Tutorial with ExamplesE2MATRIX The document provides a comprehensive tutorial on Verilog HDL, covering crucial aspects such as simulation, synthesis, modules, and various language constructs. It includes structured examples of module declarations, instantiations, and data types, as well as language conventions and simulation time scales. Essential concepts such as signal values, operators, and expression bit widths are also discussed in detail.

Shift Registers

Shift RegistersAbhilash Nair Shift registers are digital circuits composed of flip-flops that can shift data from one stage to the next. They can be configured for serial-in serial-out, serial-in parallel-out, parallel-in serial-out, or parallel-in parallel-out data movement. Common applications include converting between serial and parallel data, temporary data storage, and implementing counters. MSI shift registers like the 74LS164 and 74LS166 provide 8-bit shift register functionality.

gate level modeling

gate level modelingVandanaBR2 This document describes gate level modeling in Verilog. It discusses gate types like AND, OR, and NOT gates that can be used as primitives. It describes how to instantiate gates and provides examples of instantiating gates like NAND and AND gates. It also describes structural modeling of circuits like a 2-input multiplexer, full adder, D latch, and master-slave JK flip-flop using gate level primitives.

Experiment write-vhdl-code-for-realize-all-logic-gates

Experiment write-vhdl-code-for-realize-all-logic-gatesRicardo Castro The document describes an experiment to write VHDL code for basic logic gates. It includes the truth tables, logic diagrams, and VHDL code for AND, OR, NOT, NAND, NOR, and EXOR gates. Waveform diagrams are provided to simulate the behavior of each gate.

DESIGN AND SIMULATION OF DIFFERENT 8-BIT MULTIPLIERS USING VERILOG CODE BY SA...

DESIGN AND SIMULATION OF DIFFERENT 8-BIT MULTIPLIERS USING VERILOG CODE BY SA...Saikiran Panjala This document describes the design and simulation of different 8-bit multipliers using Verilog code. It summarizes four multipliers: array, Wallace tree, Baugh-Wooley, and Vedic. It finds that the Baugh-Wooley multiplier has advantages in speed, delay, area, complexity, and power consumption compared to the other multipliers. The document also discusses half adders, full adders, ripple carry adders, carry save adders, and multiplication algorithms. It aims to compare the multipliers based on area, speed, and delay.

More Related Content

What's hot (20)

Verilog Tasks and functions

Verilog Tasks and functionsVinchipsytm Vlsitraining The document outlines the use of tasks and functions in Verilog HDL, emphasizing their purpose in behavioral modeling and code reuse. Functions return a single value without timing control, while tasks can have timing controls and multiple input/output arguments. Key differences and examples of their declaration and invocation are also provided.

VHDL- gate level modelling

VHDL- gate level modellingVandanaPagar1 This document provides an overview of Verilog hardware description language (HDL) and gate-level modeling. It discusses the key components of Verilog modules like module definition, ports, parameters and instantiations. It describes how to define ports and connect ports in a module. It also covers different gate primitives in Verilog like AND, OR, NOT etc. and how to describe gate-level designs using these primitives by specifying gate connections and delays. Finally, it mentions some references for further reading on Verilog HDL and digital logic design.

Interfacing methods of microcontroller

Interfacing methods of microcontrollerDiwaker Pant The document discusses microcontroller interfacing. It defines interfacing as the transfer of data between microcontrollers and peripherals using buses. Interfacing is needed to connect a microcontroller's computation capabilities to external signals or devices to enable man-machine interaction. Various interfacing methods are described, including wiring techniques like wires, buses, and pins. Examples of interfacing a microcontroller to memory and I/O devices are provided. Common microcontroller interfaces like digital input/output, analog, serial interfaces are also summarized along with their applications and advantages/disadvantages.

module1:Introduction to digital electronics

module1:Introduction to digital electronicschandrakant shinde The document provides an overview of the Analog and Digital Electronics course taught at Matoshri College of Engineering & Research Centre. It includes information about the course's teaching scheme, examination scheme, objectives, and outcomes. The objectives are to design logical, sequential and combinational digital circuits using K-maps and to develop concepts related to operational amplifiers and rectifiers. The document also provides details of the topics to be covered in the first unit including Boolean algebra, K-maps, and the design of combinational circuits. It introduces concepts such as logic gates, number systems, and digital signals.

Digital electronics logic families

Digital electronics logic familiesBLESSINAR0 This document provides an overview of different digital logic families. It begins by introducing logic gates and integrated circuits. It then classifies logic families as either bipolar or unipolar, and lists examples of each. Key specifications of digital ICs are defined, including propagation delay, fan-in/fan-out, input/output logic levels, and noise margin. Transistor-transistor logic (TTL) and complementary metal-oxide-semiconductor (CMOS) circuits are described. The TTL NAND gate uses multiple emitter transistors while the CMOS NAND gate uses both P-channel and N-channel MOSFETs. Emitter-coupled logic (ECL) provides the fastest

Magnitude comparator

Magnitude comparatorSyed Saeed - The document discusses magnitude comparators, which are used to compare two binary numbers and output whether the first number is less than, equal to, or greater than the second number.

- It explains 1-bit and 2-bit magnitude comparators, providing their truth tables and logic diagrams. For a 1-bit comparator, it derives the logic expressions for the three outputs using K-maps.

- For a 2-bit comparator, it similarly provides the truth table and derives the K-map expressions for the three outputs. It then shows the full logic diagram for a 2-bit magnitude comparator using AND, OR, and NOT gates.

verilog code for logic gates

verilog code for logic gatesRakesh kumar jha The document contains Verilog code for half adders and full adders. It provides two implementations for each: a half adder is implemented using XOR and AND gates to calculate the sum and carry outputs from two input bits, and a full adder uses additional gates to calculate the sum and carry from three input bits.

Basics of digital verilog design(alok singh kanpur)

Basics of digital verilog design(alok singh kanpur)Alok Singh The document discusses the use of Verilog, a hardware description language (HDL), for digital design, emphasizing its importance as designs grow more complex. It compares Verilog with VHDL, detailing the advantages of its concise syntax and hierarchical modeling capabilities. The document covers various abstraction levels in HDLs, highlighting the transition from gate-level designs to higher-level behavioral models for efficient verification and synthesis.

Verilog Test Bench

Verilog Test BenchDr.YNM The document discusses the process of verifying a chip's design using a Verilog testbench, which is a HDL code that applies input stimuli to the design under test (DUT) and captures its output for comparison with expected results. It outlines the structure and steps for creating a testbench, including initializing inputs, generating test vectors, and checking the DUT's behavior against predefined outputs. The document also provides examples of testbenches for various digital circuits, such as NAND gates, half-adders, and full-adders.

Encoder

EncoderMahmudul Hasan This presentation introduces encoders. It discusses that an encoder is a combinational circuit that performs the reverse operation of a decoder, with a maximum of 2n inputs and n outputs. The simplest encoder is a 2n-to-n binary encoder, where one of the 2n inputs is 1 and the output is an n-bit binary number representing the activated input. An example of an 8-to-3 binary encoder is shown, where only one of the 8 inputs can be activated at a time, and the 3 outputs represent the activated input in binary code.

Complex Programmable Logic Device (CPLD) Architecture and Its Applications

Complex Programmable Logic Device (CPLD) Architecture and Its Applicationselprocus A Complex Programmable Logic Device (CPLD) is an integrated circuit used to implement digital logic, characterized by multiple programmable logic blocks that can handle more complex designs than Simple Programmable Logic Devices (SPLDs) but less than Field Programmable Gate Arrays (FPGAs). CPLDs are ideal for high-performance applications and are often utilized in portable devices due to their low power consumption and small size. They can be programmed using languages like Verilog or VHDL, with the design process involving simulation, synthesis, and a place-and-route stage to fit the architecture.

Multiplexers & Demultiplexers

Multiplexers & DemultiplexersJayanshu Gundaniya Multiplexers and demultiplexers allow digital information from multiple sources to be routed through a single line. A multiplexer has multiple data inputs, select lines to choose an input, and a single output. A demultiplexer has a single input, select lines to choose an output, and multiple outputs. Bigger multiplexers and demultiplexers can be built by cascading smaller ones. Multiplexers can implement logic functions by using the select lines as variables and routing the input lines to the output.

Verilog HDL

Verilog HDLMantra VLSI This document provides an introduction to Verilog HDL including:

- An overview of Verilog keywords, data types, abstraction levels, and design methodology.

- Details on the history of Verilog including its development over time and transitions to newer standards.

- Explanations of key Verilog concepts like modules, ports, instantiation, stimuli, and lexical conventions.

Modules are the basic building blocks, ports define module interfaces, and instantiation replicates modules. Stimuli provide test inputs and lexical conventions cover syntax rules.

Transistor Transistor Logic

Transistor Transistor Logicsurat murthy The document provides an overview of transistor-transistor logic (TTL) and its applications in digital circuits, detailing the evolution and variations of TTL technology since its introduction in 1963. It explains different TTL sub-families, their characteristics such as power dissipation and speed, and comparisons with other logic families like resistor-transistor logic and CMOS. Additionally, it outlines key parameters like propagation delay and speed-power product that are crucial for evaluating TTL performance.

Sequence detector Verilog Code

Sequence detector Verilog CodeBharti Airtel Ltd. This document describes an experiment to implement a sequence detector using behavioral modeling. The sequence detector will output a 1 when it detects the input sequence of 11011. It includes the state transition diagram for detecting the 1011 sequence and the Verilog code for the sequence detector module. The code defines the different states like s0, s1, etc. and uses case statements to transition between the states based on the current input and update the output. The learning outcome is understanding how to detect a sequence step-by-step and learning Xilinx software commands.

boolean algebra and logic simplification

boolean algebra and logic simplificationUnsa Shakir The document provides an overview of Boolean algebra and logic simplification. It covers topics such as Boolean variables that can take true/false or 1/0 values, basic logic gates like AND, OR, NOT, NAND and NOR gates, canonical forms including sum-of-products and product-of-sums, De Morgan's laws, and examples of simplifying Boolean expressions and implementing logic circuits.

Verilog Tutorial - Verilog HDL Tutorial with Examples

Verilog Tutorial - Verilog HDL Tutorial with ExamplesE2MATRIX The document provides a comprehensive tutorial on Verilog HDL, covering crucial aspects such as simulation, synthesis, modules, and various language constructs. It includes structured examples of module declarations, instantiations, and data types, as well as language conventions and simulation time scales. Essential concepts such as signal values, operators, and expression bit widths are also discussed in detail.

Shift Registers

Shift RegistersAbhilash Nair Shift registers are digital circuits composed of flip-flops that can shift data from one stage to the next. They can be configured for serial-in serial-out, serial-in parallel-out, parallel-in serial-out, or parallel-in parallel-out data movement. Common applications include converting between serial and parallel data, temporary data storage, and implementing counters. MSI shift registers like the 74LS164 and 74LS166 provide 8-bit shift register functionality.

gate level modeling

gate level modelingVandanaBR2 This document describes gate level modeling in Verilog. It discusses gate types like AND, OR, and NOT gates that can be used as primitives. It describes how to instantiate gates and provides examples of instantiating gates like NAND and AND gates. It also describes structural modeling of circuits like a 2-input multiplexer, full adder, D latch, and master-slave JK flip-flop using gate level primitives.

Viewers also liked (10)

Experiment write-vhdl-code-for-realize-all-logic-gates

Experiment write-vhdl-code-for-realize-all-logic-gatesRicardo Castro The document describes an experiment to write VHDL code for basic logic gates. It includes the truth tables, logic diagrams, and VHDL code for AND, OR, NOT, NAND, NOR, and EXOR gates. Waveform diagrams are provided to simulate the behavior of each gate.

DESIGN AND SIMULATION OF DIFFERENT 8-BIT MULTIPLIERS USING VERILOG CODE BY SA...

DESIGN AND SIMULATION OF DIFFERENT 8-BIT MULTIPLIERS USING VERILOG CODE BY SA...Saikiran Panjala This document describes the design and simulation of different 8-bit multipliers using Verilog code. It summarizes four multipliers: array, Wallace tree, Baugh-Wooley, and Vedic. It finds that the Baugh-Wooley multiplier has advantages in speed, delay, area, complexity, and power consumption compared to the other multipliers. The document also discusses half adders, full adders, ripple carry adders, carry save adders, and multiplication algorithms. It aims to compare the multipliers based on area, speed, and delay.

【掌握】數位邏輯(含實習)複習講義電子試閱本

【掌握】數位邏輯(含實習)複習講義電子試閱本lungtengtech 本书是一本关于数字逻辑的复习教材,涵盖了理论与实践,通过重点整理、经典试题和图表分析帮助学生掌握高中统测的命题趋势与重点。主要章节包括数字系统、基本逻辑门、布尔代数和组合逻辑等,全面解析了各个主题并提供过往考试题目以增强解题技巧。特色在于图表化整理和系统的复习方式,使学习过程更加清晰和高效。

Verilog Lecture3 hust 2014

Verilog Lecture3 hust 2014Béo Tú This document discusses different types of simulation for digital circuits including analog simulation using a SPICE engine, digital simulation, and event-driven simulation. It also covers testbenches, including generating stimulus, monitoring outputs, and exhaustively testing designs. Key topics covered include clocks, finite state machine testing, and force/release in testbenches.

DESIGN AND PERFORMANCE ANALYSIS OF BINARY ADDERS_edited

DESIGN AND PERFORMANCE ANALYSIS OF BINARY ADDERS_editedShital Badaik The document describes the design and performance analysis of various binary adders. It discusses the design of ripple carry adders of sizes 4-bit, 8-bit and 16-bit. The designs are implemented using Verilog HDL and simulated using Xilinx ISE simulator. The performance parameters like area and delay are determined and compared for different adder designs including carry look ahead adder, carry select adder, carry skip adder, carry increment adder and carry save adder.

VHDL

VHDLRamasubbu .P The document provides an introduction to VHDL including its origins, domains of description, abstraction levels, modeling styles, and examples of behavioral and structural descriptions. It discusses key VHDL concepts such as entities, architectures, concurrency, hierarchy, and modeling at different levels of abstraction using both behavioral and structural descriptions. Examples include behavioral descriptions of basic components like an AND gate, full adder, D flip-flop, and 4-to-1 multiplexer as well as structural descriptions of a 4-bit adder and 4-bit comparator.

BCD ADDER

BCD ADDER United International University This document presents information about adders and binary coded decimal (BCD) adders. It defines half adders and full adders, which are computational devices that add binary digits and produce sum and carry outputs. It also explains what a BCD adder is and how it adds two 4-bit BCD digits while handling carries such that the result is always a valid BCD number between 0-9. The document provides examples of BCD addition and conversions between binary and BCD formats. It concludes with some applications of BCD adders in areas like digital displays and counters.

Bit Serial multiplier using Verilog

Bit Serial multiplier using VerilogBhargavKatkam This document describes a bit-serial multiplier project implemented using Verilog HDL. It discusses bit-serial arithmetic and its advantages over parallel multipliers. The project involves designing and simulating a bit-serial multiplier using a Xilinx tool. The multiplier is tested to verify correct functionality.

Programs of VHDL

Programs of VHDLRkrishna Mishra The document contains 7 VHDL programs with the following objectives:

1) Implement a 3:8 decoder using behavioral modeling.

2) Implement an 8:1 multiplexer using behavioral modeling.

3) Implement a 1:8 demultiplexer using behavioral modeling.

4) Implement 4-bit addition/subtraction.

5) Implement a 4-bit comparator.

6) Generate a MOD-10 up counter.

7) Generate a 1010 sequence detector.

Each program contains the VHDL code, RTL logic diagram and output waveform to achieve the given objective.

8 bit alu design

8 bit alu designShobhan Pujari The document outlines a project aimed at designing an 8-bit arithmetic logic unit (ALU) that processes two 8-bit binary numbers and performs various arithmetic, logical, and relational operations using Verilog code. It discusses the historical context of the ALU, starting from John von Neumann's concept in 1945 to its evolution and significance in microprocessors. Additionally, it emphasizes teamwork in achieving the project goal and mentions the potential of using reversible logic gates for enhanced efficiency.

Ad

Similar to Coding verilog (20)

Verilog Final Probe'22.pptx

Verilog Final Probe'22.pptxSyedAzim6 Verilog is a hardware description language used to design digital circuits. It allows designs to be described at different levels of abstraction, from behavioral to gate level. At the behavioral level, algorithms and dataflow are described. Modules define design entities and are instantiated within other modules. Always and initial blocks specify concurrent and sequential procedural blocks. Dataflow and gate-level modeling instantiate primitives like logic gates. Verilog supports procedural assignments, parameters, user-defined tasks and functions, and testbenches for simulation.

a verilog presentation for deep concept understa

a verilog presentation for deep concept understaSRAJALDWIVEDI1 The document provides an extensive overview of Verilog HDL (Hardware Description Language) and its applications in digital circuit design and verification. It explains the necessity for HDLs in automating complex circuit designs, details syntactical elements, data types, modules, and their instantiation, as well as the different types of variable assignments and procedural constructs in Verilog. Additionally, it covers design issues such as synthesis, reset types, parameters, and timing considerations in circuit design.

Verilog Lecture2 thhts

Verilog Lecture2 thhtsBéo Tú This document contains lecture notes on Verilog syntax and structural modeling. It discusses various Verilog concepts like commenting code, numbers and identifiers, vectors, arrays, parameters and defines, gate primitives, and hierarchy. It provides examples of modeling half adders and full adders structurally and behaviorally using primitives, modules, and always blocks. The document emphasizes choosing descriptive names and commenting code to explain the purpose or motivation behind design decisions.

Verilogforlab

VerilogforlabShankar Bhukya Verilog is a hardware description language used to model and simulate digital circuits. It supports different levels of abstraction from algorithmic level down to transistor level. The document describes key Verilog concepts including data types, operators, procedural blocks, timing, and system tasks. It also explains the use of modules for hierarchical design and compiler directives for code reuse and timescale specification.

Verilog_ppt.pdf

Verilog_ppt.pdfApurbaDebnath8 This document provides an introduction to Verilog fundamentals including:

- A brief history of hardware description languages and their role in digital design flow from schematics to automatic place and route tools.

- An overview of how FPGAs are programmed using a hardware description language like Verilog by synthesizing the behavioral or register transfer level description.

- An explanation of basic Verilog constructs like modules, ports, always blocks, variables, operators for implementing combinational and sequential logic.

- Examples of coding a 4-bit counter and decoder module in Verilog and connecting them in a top module.

System Verilog Tutorial - VHDL

System Verilog Tutorial - VHDLE2MATRIX This document provides an overview of System Verilog concepts including simulation and synthesis, modules and primitives, styles, data types, operators, and more. Key points covered include the module concept as the basic design unit, module declaration syntax, module instantiation, different styles like structural, RTL/dataflow and behavioral, data types for nets and registers, number representation formats, and basic Verilog operators. The document serves as a tutorial introduction to essential System Verilog language constructs.

verilog

verilogShrikant Vaishnav This document contains slides from a lecture on Verilog hardware description language. It introduces Verilog and compares it to other HDLs like VHDL. It discusses both structural and behavioral modeling in Verilog. Structural models describe a design using primitive components and their interconnections, while behavioral models describe the input-output function of a design. The document provides examples of modeling combinational logic like an AND gate and sequential logic like a 4-bit comparator using behavioral and structural Verilog. It also covers Verilog syntax like modules, ports, continuous assignments, always blocks, if/case statements.

Verilogspk1

Verilogspk1supriya kurlekar Verilog and VHDL are hardware description languages used to design digital circuits. Verilog was developed starting in 1985 and became an IEEE standard in 1995. VHDL was developed for the US Department of Defense starting in 1981 and also became an IEEE standard. Both languages use syntax similar to C and allow designers to describe circuits at different levels, from behavioral to structural descriptions using logic gates and modules. They support data types like nets, registers, vectors, and integers to model hardware. Common constructs include modules, ports, continuous assignments, procedural blocks, and instantiating lower-level modules.

Verilog_Overview.pdf

Verilog_Overview.pdfQuangHuyDo3 Verilog is a hardware description language used to model digital circuits. It was created in 1984 and became an IEEE standard in 1995. This document discusses Verilog modules, data types, operators, modeling techniques like behavioral and structural, and procedural statements like always and initial blocks. Verilog allows hierarchical design by defining smaller modules that can be instantiated in larger modules.

Short Notes on Verilog and SystemVerilog

Short Notes on Verilog and SystemVerilogJason J Pulikkottil Verilog is a software language initially designed for digital logic simulation that is now widely used for hardware design, particularly for ASICs and FPGAs. It incorporates both structural and behavioral modeling, allowing easy combination of descriptive models and testbenches. Key components include behavioral processes like always blocks and structural representations through modules, and it supports four-valued logic to model real-world electronic states.

SKEL 4273 CAD with HDL Topic 2

SKEL 4273 CAD with HDL Topic 2alhadi81 The document serves as an introduction to Verilog HDL, detailing its basic structures, modeling styles, and constructs. It outlines the evolution of Verilog from its original 1995 standard to the enhanced 2001 version, highlighting its application in both simulation and synthesis of digital hardware. Additionally, it explains various data types, operators, and the different modeling styles (structural, dataflow, and behavioral) used in digital circuit design.

verilog ppt .pdf

verilog ppt .pdfRavinaBishnoi8 The Verilog language was originally developed as a modeling language for digital logic simulation. It has since become one of the two most commonly used languages for digital hardware design, along with VHDL. Verilog supports both structural and behavioral modeling styles. It uses modules to represent hardware components, which can contain instances of other modules or behavioral code like always blocks. Verilog simulations are event-driven and support both combinational and sequential logic modeling.

Verilog

Verilogabkvlsi Verilog is a hardware description language (HDL) used to model electronic systems. Some key points:

- Verilog originated in 1983 and was standardized as IEEE 1364. It is used to model digital circuits at different levels of abstraction from algorithmic to switch levels.

- Modules are the basic building blocks in Verilog. Designs are constructed in a hierarchical manner using instances of modules.

- Common constructs in Verilog include nets, registers, parameters, tasks, always and initial blocks, and data types like wire and reg.

- Basic gates and larger components like decoders, multiplexers, and adders can be modeled at the gate level in Verilog. Different adder architectures like

Verilog_Cheat_sheet_1672542963.pdf

Verilog_Cheat_sheet_1672542963.pdfsagar414433 Verilog is a hardware description language commonly used for designing digital circuits. It allows both structural and behavioral modeling. Structurally, Verilog programs are built from modules containing instances of other modules or primitives. Behaviorally, modules contain initial and always blocks with imperative code. The always blocks model concurrent hardware processes that execute when signals change. Verilog supports both combinational logic with continuous assignments and sequential logic with blocking assignments in always blocks.

Verilog_Cheat_sheet_1672542963.pdf

Verilog_Cheat_sheet_1672542963.pdfsagar414433 Verilog is a hardware description language commonly used for designing digital circuits. It allows both structural and behavioral modeling. Structurally, Verilog programs are built from modules containing instances of other modules or primitives. Behaviorally, modules contain initial and always blocks that use imperative code like assignments and conditionals. Verilog simulations execute events concurrently using a discrete event queue to model digital hardware behavior.

Verilog Cheat sheet-2 (1).pdf

Verilog Cheat sheet-2 (1).pdfDrViswanathKalannaga1 Verilog is a hardware description language commonly used for designing digital circuits. It supports both structural and behavioral modeling styles. Structural modeling involves describing a design using instances of modules and primitives, while behavioral modeling uses procedural code like always blocks. Verilog supports various data types including nets, regs, vectors, and user-defined types. It also has a four-value logic system. Testbenches provide stimulus and check results of simulated designs.

Ad

More from umarjamil10000 (8)

Galvanometer,wheatstone bridge,ohm law,

Galvanometer,wheatstone bridge,ohm law,umarjamil10000 The document describes the Wheatstone bridge, an electrical circuit used to determine unknown resistances by connecting four resistors in a closed loop with a sensitive galvanometer. A balanced Wheatstone bridge occurs when no current flows through the galvanometer, indicating equal potential at its terminals. Various devices for measuring resistance, such as the meter bridge and potentiometer, are based on the principles of the Wheatstone bridge.

Mechatronics, Embedded System,

Mechatronics, Embedded System,umarjamil10000 Embedded systems combine hardware and software to form components of larger machines. Mechatronics is the synergistic combination of precision engineering, electronics, and control systems in products and processes. The document discusses future career opportunities in embedded systems, mechatronics, and control, including in automotive and aerospace industries, medicine, robotics, manufacturing, and telecommunications. These fields will revolutionize technology by combining mechanics, electronics, software, and control systems to create smart systems like driverless cars, medical robots, and more. Broadly trained engineers will be needed to develop new technologies and take advantage of exciting career prospects.

Electric Field

Electric Fieldumarjamil10000 1. A field is defined as a property of space in which a material object experiences a force. For example, above the earth there is a gravitational field where a mass experiences a downward force.

2. The electric field is a vector field that exists around an electric charge even when no other charges are present. The direction of the electric field points away from a positive charge and towards a negative charge.

3. The electric field strength is defined as the force experienced by a hypothetical positive test charge per unit of charge, located at that point in space.

Image denoising

Image denoising umarjamil10000 The document discusses the limitations of imaging technology, focusing on issues such as noise interference and blur that complicate the acquisition of high-quality images, especially in non-visible and micro/macro scales. It elaborates on various types of noise, particularly impulse noise and additive white Gaussian noise, and details noise removal techniques, including median filtering and linear filtering, while addressing their effectiveness and drawbacks. The document also covers concepts like stochastic resonance, noise modeling, and takes a deep dive into image denoising methods using different filtering approaches.

Matlab dsp examples

Matlab dsp examplesumarjamil10000 The document contains MATLAB code for digital signal processing programs including:

1) Bandpass filters, Kaiser window functions, time domain windows, DFT of square waves with different duties, notch filters, and resonators.

2) Comb filters and the Welch method for calculating the power spectral density of a noisy signal.

3) A discrete Fourier transform program that calculates the forward and inverse DFT using twiddle factors.

noise removal in matlab

noise removal in matlabumarjamil10000 This document discusses working with sound in Matlab and Cogent. It covers loading and playing sounds, creating sounds of different frequencies and amplitudes, combining sounds, and plotting sound waves. Key steps include reading and writing .wav files, configuring sound in Cogent, generating sine waves of different frequencies to create melodies, and manipulating amplitude to make sounds louder or quieter. Functions mentioned include wavread, sound, wavwrite, config_sound, loadsound, playsound, waitsound, sin, and plot.

Pm project

Pm projectumarjamil10000 The document describes an advertising project for Orient Advertising Company. The project was to create a television advertisement for Mobilink featuring actor Ali Zafar. Due to scheduling conflicts, Ali Zafar replaced Shan for the lead role. Shooting plans were changed from outdoor to indoor locations due to difficulties coordinating the cast and crew. Graphics were added to depict different socioeconomic classes. The finished ad was approved by Mobilink and broadcast on television channels.

Mechatronics systems

Mechatronics systemsumarjamil10000 This document provides an overview of mechatronics systems and their applications across multiple domains. It defines mechatronics as the synergistic combination of mechanical, electrical, and computer engineering. Examples of mechatronics applications discussed include microfactories, CNC machining, automobiles, high-speed trains, robots, medical devices, defense technologies, smart homes, and more. Across these diverse areas, mechatronics integrates mechanical and electronic engineering to create automated systems that sense and control physical processes.

Recently uploaded (20)

HistoPathology Ppt. Arshita Gupta for Diploma

HistoPathology Ppt. Arshita Gupta for Diplomaarshitagupta674 Hello everyone please suggest your views and likes so that I uploaded more study materials

In this slide full HistoPathology according to diploma course available like fixation

Tissue processing , staining etc

Gladiolous Cultivation practices by AKL.pdf

Gladiolous Cultivation practices by AKL.pdfkushallamichhame This includes the overall cultivation practices of Rose prepared by:

Kushal Lamichhane (AKL)

Instructor

Shree Gandhi Adarsha Secondary School

Kageshowri Manohara-09, Kathmandu, Nepal

Code Profiling in Odoo 18 - Odoo 18 Slides

Code Profiling in Odoo 18 - Odoo 18 SlidesCeline George Profiling in Odoo identifies slow code and resource-heavy processes, ensuring better system performance. Odoo code profiling detects bottlenecks in custom modules, making it easier to improve speed and scalability.

VCE Literature Section A Exam Response Guide

VCE Literature Section A Exam Response Guidejpinnuck This practical guide shows students of Unit 3&4 VCE Literature how to write responses to Section A of the exam. Including a range of examples writing about different types of texts, this guide:

*Breaks down and explains what Q1 and Q2 tasks involve and expect

*Breaks down example responses for each question

*Explains and scaffolds students to write responses for each question

*Includes a comprehensive range of sentence starters and vocabulary for responding to each question

*Includes critical theory vocabulary lists to support Q2 responses

How to Manage Different Customer Addresses in Odoo 18 Accounting

How to Manage Different Customer Addresses in Odoo 18 AccountingCeline George A business often have customers with multiple locations such as office, warehouse, home addresses and this feature allows us to associate with different addresses with each customer streamlining the process of creating sales order invoices and delivery orders.

Pests of Maize: An comprehensive overview.pptx

Pests of Maize: An comprehensive overview.pptxArshad Shaikh Maize is susceptible to various pests that can significantly impact yields. Key pests include the fall armyworm, stem borers, cob earworms, shoot fly. These pests can cause extensive damage, from leaf feeding and stalk tunneling to grain destruction. Effective management strategies, such as integrated pest management (IPM), resistant varieties, biological control, and judicious use of chemicals, are essential to mitigate losses and ensure sustainable maize production.

K12 Tableau User Group virtual event June 18, 2025

K12 Tableau User Group virtual event June 18, 2025dogden2 National K12 Tableau User Group: June 2025 meeting slides

How to use search fetch method in Odoo 18

How to use search fetch method in Odoo 18Celine George The search_fetch is a powerful ORM method used in Odoo for some specific addons to combine the functionality of search and read for more efficient data fetching. It might be used to search for records and fetch specific fields in a single call. It stores the result in the cache memory.

M&A5 Q1 1 differentiate evolving early Philippine conventional and contempora...

M&A5 Q1 1 differentiate evolving early Philippine conventional and contempora...ErlizaRosete MAPEH 6 QI WEEK I

A Visual Introduction to the Prophet Jeremiah

A Visual Introduction to the Prophet JeremiahSteve Thomason These images will give you a visual guide to both the context and the flow of the story of the prophet Jeremiah. Feel free to use these in your study, preaching, and teaching.

IIT KGP Quiz Week 2024 Sports Quiz (Prelims + Finals)

IIT KGP Quiz Week 2024 Sports Quiz (Prelims + Finals)IIT Kharagpur Quiz Club The document outlines the format for the Sports Quiz at Quiz Week 2024, covering various sports & games and requiring participants to Answer without external sources. It includes specific details about question types, scoring, and examples of quiz questions. The document emphasizes fair play and enjoyment of the quiz experience.

LDMMIA Yoga S10 Free Workshop Grad Level

LDMMIA Yoga S10 Free Workshop Grad LevelLDM & Mia eStudios This is complete for June 17th. For the weekend of Summer Solstice

June 20th-22nd.

6/17/25: “My now Grads, You’re doing well. I applaud your efforts to continue. We all are shifting to new paradigm realities. Its rough, there’s good and bad days/weeks. However, Reiki with Yoga assistance, does work.”

6/18/25: "For those planning the Training Program Do Welcome. Happy Summer 2k25. You are not ignored and much appreciated. Our updates are ongoing and weekly since Spring. I Hope you Enjoy the Practitioner Grad Level. There's more to come. We will also be wrapping up Level One. So I can work on Levels 2 topics. Please see documents for any news updates. Also visit our websites. Every decade I release a Campus eMap. I will work on that for summer 25. We have 2 old libraries online thats open. https://ldmchapels.weebly.com "

Our Monthly Class Roster is 7,141 for 6/21.

ALL students get privacy naturally. Thx Everyone.

As a Guest Student,

You are now upgraded to Grad Level.

See Uploads for “Student Checkins” & “S9”. Thx.

Happy Summer 25.

These are also timeless.

Thank you for attending our workshops.

If you are new, do welcome.

For visual/Video style learning see our practitioner student status.

This is listed under our new training program. Updates ongoing levels 1-3 this summer. We just started Session 1 for level 1.

These are optional programs. I also would like to redo our library ebooks about Hatha and Money Yoga. THe Money Yoga was very much energy healing without the Reiki Method. An updated ebook/course will be done this year. These Projects are for *all fans, followers, teams, and Readers. TY for being presenting.

This is why students from these 44 institutions have not received National Se...

This is why students from these 44 institutions have not received National Se...Kweku Zurek This is why students from these 44 institutions have not received National Service PIN codes (LIST)

How to Customize Quotation Layouts in Odoo 18

How to Customize Quotation Layouts in Odoo 18Celine George Customizing quotation layouts in Odoo 18 allows businesses to personalize their quotations to match branding or specific requirements. This can include adding logos, custom fields, or modifying headers and footers.

LDMMIA Shop & Student News Summer Solstice 25

LDMMIA Shop & Student News Summer Solstice 25LDM & Mia eStudios 6/18/25

Shop, Upcoming: Final Notes to Review as we Close Level One. Make sure to review the orientation and videos as well. There’s more to come and material to cover in Levels 2-3. The content will be a combination of Reiki and Yoga. Also energy topics of our spiritual collective.

Thanks again all future Practitioner Level Students. Our Levels so far are: Guest, Grad, and Practitioner. We have had over 5k Spring Views.

https://ldm-mia.creator-spring.com

Peer Teaching Observations During School Internship

Peer Teaching Observations During School InternshipAjayaMohanty7 FOR B.ED,M.ED,M.A.EDUCATION AND ANY STUDENT OF TEACHER EDUCATION

University of Ghana Cracks Down on Misconduct: Over 100 Students Sanctioned

University of Ghana Cracks Down on Misconduct: Over 100 Students SanctionedKweku Zurek University of Ghana Cracks Down on Misconduct: Over 100 Students Sanctioned

Coding verilog

- 1. 1 Lecture 7 Verilog Structural constructs Describing combinational circuits Additional references Tutorial and reference manual are found in ActiveHDL help “Starter’s Guide to Verilog 2001” by Michael Ciletti copies for borrowing in hardware lab

- 2. 2 Combinational design Step 1: Understand the problem Identify the inputs and outputs Draw a truth table Step 2: Simplify the logic Draw a K-map Write a simplified Boolean expression SOP or POS Use don’t cares Step 3: Implement the design Logic gates and/or Verilog

- 3. 3 Ways of specifying circuits Schematics Structural description Describe circuit as interconnected elements Build complex circuits using hierarchy Large circuits are unreadable Hardware description languages (HDLs) Not programming languages Parallel languages tailored to digital design Synthesize code to produce a circuit

- 4. 4 Verilog versus VHDL Both “IEEE standard” languages Most tools support both Verilog is “simpler” Less syntax, fewer constructs VHDL is more structured Can be better for large, complex systems Better modularization

- 5. 5 Simulation and synthesis Simulation Models what a circuit does Multiply is “*”, ignoring implementation options Allows you to test design options “Execute” a design to verify correctness Synthesis Converts your code to a "netlist" Can simulate synthesized design Tools map your netlist to hardware

- 6. 6 Simulation and synthesis Simulation and synthesis in the CSE curriculum CSE370: Learn simulation CSE467: Learn synthesis Synthesis HDL Description Gate or Transistor Description Simulation Simulation Physical Implementation Functional Validation Functional/ Timing Validation Real Chip!

- 7. 7 Simulation You provide an environment Using non-circuit constructs Active-HDL waveforms, read files, print Using Verilog simulation code A “test fixture” Simulation Test Fixture (Specification) Circuit Description (Synthesizable)

- 8. 8 E C g2 Y A B g1 g3 X 2 NOT 1 AND2 3 OR2 Specifying circuits in Verilog Three major styles Instances and wires Continuous assignments “always” blocks wire E; and g1(E,A,B); not g2(Y,C); or g3(X,E,Y); wire E; assign E = A & B; assign Y = ~C; assign X = E | Y; reg E, X, Y; always @ (A or B or C) begin E = A & B; Y = ~C; X = E | Y; end “Structural” “Behavioral”

- 9. 9 Data types Values on a wire 0, 1, x (unknown or conflict), z (tristate or unconnected) Vectors A[3:0] vector of 4 bits: A[3], A[2], A[1], A[0] Unsigned integer value Indices must be constants

- 10. 10 Manipulating vectors Concatenating bits/vectors, use { } e.g. sign extend B[7:0] = {A[3], A[3], A[3], A[3], A[3:0]}; B[7:0] = {4{A[3]}, A[3:0]}; Style: Use a[7:0] = b[7:0] + c[7:0] Not a = b + c;

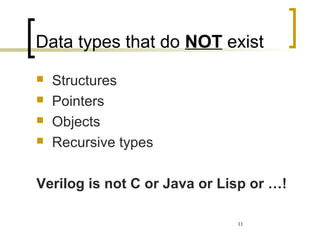

- 11. 11 Data types that do NOT exist Structures Pointers Objects Recursive types Verilog is not C or Java or Lisp or …!

- 12. 12 Numbers Format: <sign><size><base><number> 14 Decimal number –4’b11 4-bit 2’s complement binary of 0011 (is 1101) 12’b0000_0100_0110 12 bit binary number (_ is ignored) 12’h046 3-digit (12-bit) hexadecimal number

- 13. 13 Numbers are unsigned C[4:0] = A[3:0] + B[3:0]; if A = 0110 (6) and B = 1010(–6), then C = 10000 (not 00000) B is zero-padded, not sign-extended

- 14. 14 Operators Similar to Java operators

- 15. 15 Two abstraction mechanisms Modules More structural, but also behavioral Heavily used in 370 and “real” Verilog code Functions More behavioral Used to some extent in “real” Verilog, but not much in 370

- 16. 16 Basic building blocks: modules // first simple example module simple (X,Y,A,B,C); input A,B,C; output X,Y; wire E and g1(E,A,B); not g2(Y,C); or g3(X,E,Y); endmodule E C g2 Y A B g1 g3 X 2 NOT 1 AND2 3 OR2

- 17. 17 Basic building blocks: modules Instanced into a design Never called Use wires for connections Modules execute in parallel Gate declarations (and, or, etc) List outputs first Inputs second Name can’t begin with a number Names are case sensitive Keywords are in lowercase and, or, not are keywords Illegal to nest module definitions // for comments

- 18. 18 Modules are circuit components Module has ports External connections A,B,C,X,Y in example Port types input output inout (tristate) Use assign statements for Boolean expressions and ⇔ & or ⇔ | not ⇔ ~ // previous example as a // Boolean expression module simple2 (X,Y,A,B,C); input A,B,C; output X,Y; assign X = (A&B)|~C; assign Y = ~C; endmodule E C g2 Y A B g1 g3 X 2 NOT 1 AND2 3 OR2

- 19. 19 bbar t2 t1 abar b invb a and2 a inva b and1 or1 out 5 NOT 7 AND2 4 NOT 6 AND2 8 OR2 Structural Verilog module xor_gate (out,a,b); input a,b; output out; wire abar, bbar, t1, t2; not inva (abar,a); not invb (bbar,b); and and1 (t1,abar,b); and and2 (t2,bbar,a); or or1 (out,t1,t2); endmodule 8 basic gates (keywords): and, or, nand, nor buf, not, xor, xnor

- 20. 20 Behavioral Verilog Describe circuit behavior Not implementation A B Cin Cout Sum Adder module full_addr (Sum,Cout,A,B,Cin); input A, B, Cin; output Sum, Cout; assign {Cout, Sum} = A + B + Cin; endmodule {Cout, Sum} is a concatenation

- 21. 21 Behavioral 4-bit adder module add4 (SUM, OVER, A, B); input [3:0] A; input [3:0] B; output [3:0] SUM; output OVER; assign {OVER, SUM[3:0]} = A[3:0] + B[3:0]; endmodule “[3:0] A” is a 4-wire bus labeled “A” Bit 3 is the MSB Bit 0 is the LSB Can also write “[0:3] A” Bit 0 is the MSB Bit 3 is the LSB Buses are implicitly connected— If you write BUS[3:2], BUS[1:0], they become part of BUS[3:0]

- 22. 22 Continuous assignment Assignment is continuously evaluated Corresponds to a logic gate Assignments execute in parallel assign A = X | (Y & ~Z); assign B[3:0] = 4'b01XX; assign C[15:0] = 16'h00ff; assign #3 {Cout, Sum[3:0]} = A[3:0] + B[3:0] + Cin; gate delay (used by simulator) Boolean operators (~ for bit-wise negation) bits can assume four values (0, 1, X, Z) variables can be n-bits wide (MSB:LSB)

- 23. 23 Invalid sequential assigns assign A = X | (Y & ~Z); assign B = W | A; assign A = Y & Z; “Reusing” a variable on the left side of several assign statements is not allowed assign A = X | (Y & ~Z); assign B = W | A; assign X = B & Z; Cyclic dependencies also are bad A depends on X which depends on B which depends on A

- 24. 24 Example: 4-bit comparator module Compare1 (Equal, Alarger, Blarger, A, B); input A, B; output Equal, Alarger, Blarger; assign Equal = (A & B) | (~A & ~B); assign Alarger = (A & ~B); assign Blarger = (~A & B); endmodule Starting with 1-bit comparator Top-down design and bottom-up design are both okay Module ordering doesn’t matter because modules execute in parallel

- 25. 25 4-bit comparator // Make a 4-bit comparator from 4 1-bit comparators module Compare4(Equal, Alarger, Blarger, A4, B4); input [3:0] A4, B4; output Equal, Alarger, Blarger; wire e0, e1, e2, e3, Al0, Al1, Al2, Al3, B10, Bl1, Bl2, Bl3; Compare1 cp0(e0, Al0, Bl0, A4[0], B4[0]); Compare1 cp1(e1, Al1, Bl1, A4[1], B4[1]); Compare1 cp2(e2, Al2, Bl2, A4[2], B4[2]); Compare1 cp3(e3, Al3, Bl3, A4[3], B4[3]); assign Equal = (e0 & e1 & e2 & e3); assign Alarger = (Al3 | (Al2 & e3) | (Al1 & e3 & e2) | (Al0 & e3 & e2 & e1)); assign Blarger = (~Alarger & ~Equal); endmodule

- 26. 26 Functions Use functions for complex combinational logic module and_gate (out, in1, in2); input in1, in2; output out; assign out = myfunction(in1, in2); function myfunction; input in1, in2; begin myfunction = in1 & in2; end endfunction endmodule Benefit: Functions force a result ⇒ Compiler will fail if function does not generate a result

- 27. 27 Always code blocks reg A, B, C; always @ (W or X or Y or Z) begin A = X | (Y & ~Z); B = W | A; A = Y & Z; if (A & B) begin B = Z; C = W | Y; end end Sensitivity list: block is executed each time one of them changes value Variables that appear on the left hand side in an always block must be declared as “reg”s Statements in an always block are executed in sequence BAD: All variables must be assigned on every control path!!!

- 28. 28 Assignments Blocking assignments (Q = A) Variable is assigned immediately New value is used by subsequent statements Non-blocking assignments (Q <= A) Variable is assigned after all scheduled statements are executed Value to be assigned is computed but saved for later parallel assignment Usual use: Register assignment Registers simultaneously take new values after the clock edge

- 29. 29 Blocking vs. non-blocking Example: Swap always @(posedge CLK) begin temp = B; B = A; A = temp; end always @(posedge CLK) begin A <= B; B <= A; end

- 30. 30 Verilog tips Do not write C-code Think hardware, not algorithms Verilog is inherently parallel Compilers don’t map algorithms to circuits well Do describe hardware circuits First draw a dataflow diagram Then start coding