Computer Organization: Introduction to Microprocessor and Microcontroller

- 1. UNIT 6 Introduction to Microprocessor and Microcontroller

- 2. Microcontroller: • It’s like a small computer on a single IC. It contains a processor core, ROM, RAM and I/O pins dedicated to perform various tasks • A microcontroller can be called the heart of embedded system. • Examples: 8051, AVR, PIC series of microcontrollers.

- 3. Microprocessor: • Microprocessor has only a CPU inside them in one or few Integrated Circuits. • It is called “computer on a chip”. • Examples : Pentium, I3, and I5 etc.

- 5. Functions of Microprocessor: 1. The microprocessor is responsible for first fetching instructions from the main memory. 2. The fetched instruction is later decoded to determine the type of action that should be performed. 3. Depending on the instruction the processor has fetched it will require data from an I/O module or the main memory. 4. After that, the instruction will be executed which will require the need to carry out arithmetic or logic operations. 5. The Central Processing Unit will also supervise and control the I/O devices in addition to execution. 6. The results of the execution might need to be transferred to a memory of I/O module

- 6. Advantages of Microprocessor: • Low Cost • High Speed • Small Size • Versatile • Low Power Consumption • Less Heat Generation • Reliable • Portable

- 7. Applications of Microprocessor 1. Microprocessor is used in industry. 2. In automatic control system microcontroller can be use. 3. Car automation. 4. Telecommunication 5. Biometric 6. Radar 7. Entertainment system etc. Examples of Microprocessor: 1.Intel 4004 – The First Microprocessor 2.Intel 8085 3.Intel 8086 4.Intel Pentium 4 5.Intel Core i7 6.AMD Athlon

- 8. Pentium Architecture Block Diagram

- 10. Features of Pentium: 1. Binary Compatible with large software base: • DOS, OS, Unix and Windows 2. 32 bits Microprocessor: • 32 bit addressing • 64 bit data bus 3. Superscalar Architecture • Two pipelined Integer Unit • Capable of under one clock per Instruction • Pipelined Floating Point Unit

- 11. 4. Separate code and data caches • 8K code,8K write back data • Two way32 byte line size • Software Transparent • MESI cache consistency Protocol (Modified Exclusive Shared Invalid) 5. Advanced design features • Branch Prediction • Virtual Mode Extensions 6. Multi-Processor Support • Multiprocessor Instructions • Support for second level cache

- 12. Functional Unit 1. Integer Pipeline: • The pipelines are called “u” and “v” pipes • The U pipe can execute any instruction, while the V pipe can execute “simple” instructions as defined in the “Instruction Pairing Rules” • When instructions are paired, the instruction issued to the v-pipe is always the next sequential instruction after that one issued to u- pipe. Integer Pipeline Stages: 1. Prefetch (PF): -Instructions are prefetched from on-chip instruction cache

- 13. 2. Decode1 (D1): -Two parallel decoders attempt to decode and issue the next two sequential instructions -It decodes the instruction to generate a control word -A single control word causes direct execution of an instruction -Complex instruction require microcoded control sequencing 3. Decode2 (D2): -Decodes the Control Word -Address of memory resident operands are calculated.

- 14. 4. Execute (EX): -Instruction is executed in ALU. -Data cache is accessed at the stage -For both ALU and data cache access requires more than one clock 5. Writeback (WB): -The CPU stores the result and update the flag

- 15. 2. Floating Point Unit: • The Pentium processor FPU has 8 pipeline stages, the first five of which it shares with the integer unit 1. PF : Prefetch; 2. D1 : Instruction Decode 3. D2 : Address generation 4.EX : Memory and register read; conversion of FP data to external memory format and memory write 5. X1 : Floating Point Execute stage one; conversion of external memory format to internal FP data format and write operand to FP register file; bypass 1 6. X2 : Floating-Point Execute stage two; 7. WF : Perform rounding and write floating- point result to register file; bypass 2 8. ER : Error Reporting/Update Status Word.

- 16. 3. Cache: • The Pentium processor has two separate 8-kilobyte (KB) caches on chip, one for instructions and one for data. • It allows the Pentium processor to fetch data and instructions from the cache simultaneously

- 17. 4. Branch Target Buffer and Branch Prediction: • Branch Instruction change the normal sequential control flow of the program • Branches may be of two types: Conditional branch and unconditional branch • The Pentium processor makes the dynamic branch prediction using a Branch Target Buffer (BTB). • Pentium uses two prefetch buffers: 1. One buffer prefetches code in linear fashion 2. other prefetches instructions based on address in the branch target buffer

- 19. TLB (Translation lookaside buffers): • TLB is required only if Virtual Memory is used by a processor. In short, TLB speeds up translation of virtual address to physical address by storing page-table in a faster memory. • TLB is used by MMU when physical address needs to be translated to virtual address.

- 21. Programming Model: • processor has three operating modes 1. Real-address mode: Processors have this mode to be compatible with early Intel processors such as 8086. This mode lets the processor to address "real" memory address. It can also be called "unprotected" mode. 1. Protected mode: This is the preferred mode for a modern operating system. It allows applications to use virtual memory addressing and supports multiple programming environment and protections. 1. System management mode: This mode is designed for fast state snapshot and resumption. It is useful for power management

- 22. Register Set: Three types of registers: 1. General-purpose Registers: The eight 32-bit general-purpose data registers are used to hold operands for logical and arithmetic operations, operands for address calculations and memory pointers. EAX—Accumulator for operands and results data. EBX—Pointer to data in the DS segment. ECX—Counter for string and loop operations. EDX—I/O pointer. ESI—Pointer to data in the segment pointed to by the DS register; source pointer for string operations. EDI—Pointer to data (or destination) in the segment pointed to by the ES register; destination pointer for string operations. EBP—Pointer to data on the stack (in the SS segment). ESP—Stack pointer (in the SS segment).

- 24. 2. Segment Registers There are six segment registers that hold 16-bit segment selectors. A segment selector is a special pointer that identifies a segment in memory. The six segment registers are: * CS: code segment register * SS: stack segment register * DS, ES, FS, GS: data segment registers Four data segment registers provide programs with flexible and efficient ways to access data. 3. Status and Flag Register: • EFLAGS: The 32-bit EFLAGS register contains a group of status flags, a control flag, and a group of system flags. • EIP: The EIP register (or instruction pointer) can also be called "program counter." It contains the offset in the current code segment for the next instruction to be executed.

- 25. EFLAG Register

- 26. Register Set

- 27. Parallelism: • Computer architects are constantly striving to improve performance of the machines they design • Making the chips run faster by increasing their clock speed is one way, • However, most computer architects look to parallelism (doing two or more things at once) as a way to get even more performance for a given clock speed. • Parallelism comes in two general forms: – instruction-level parallelism, and – processor-level parallelism.

- 28. Instruction-Level Parallelism: • Parallelism is exploited within individual instructions to get more instructions/sec out of the machine. • We will consider two approached – Pipelining – Superscalar Architectures A] Pipeline: • Fetching of instructions from memory is a major bottleneck in instruction execution speed. However, computers have the ability to fetch instructions from memory in advance • These instructions were stored in a set of registers called the prefetch buffer. • Thus, instruction execution is divided into two parts: fetching and actual execution; • The concept of a pipeline carries this strategy much further. • Instead of dividing instruction execution into only two parts, it is often divided into many parts, each one handled by a dedicated piece of hardware, all of which can run in parallel.

- 30. B] Superscalar Architectures: • Going to four pipelines is conceivable, but doing so duplicates too much hardware • Instead, a different approach is used on highend CPUs. • The basic idea is to have just a single pipeline but give it multiple functional units. • This is a superscalar architecture – using more than one ALU, so that more than one instruction can be executed in parallel. • Implicit in the idea of a superscalar processor is that the S3 stage can issue instructions considerably faster than the S4 stage is able to execute them.

- 32. Processor-Level Parallelism: • Instruction-level parallelism (pipelining and superscalar operation) rarely win more than a factor of five or ten in processor speed. • To get gains of 50, 100, or more, the only way is to design computers with multiple CPUS • We will consider three alternative architectures: – Array Computers – Multiprocessors – Multicomputers

- 33. Multiprocessors: • The processing elements in an array processor are not independent CPUS, since there is only one control unit. • The first parallel system with multiple full-blown CPUs is the multiprocessor. • This is a system with more than one CPU sharing a common memory co- ordinated in software. • The simplest one is to have a single bus with multiple CPUs and one memory all plugged into it.

- 36. •8051 microcontroller is designed by Intel in 1981. •It is an 8-bit microcontroller. It is built with 40 pins DIP (dual inline package), 8 – Bit ALU: ALU or Arithmetic Logic Unit is the heart of a microcontroller. It performs arithmetic and bitwise operation on binary numbers. The ALU in 8051 is an 8 – Bit ALU i.e. it can perform operations on 8 – bit data. 8 – Bit Accumulator:The Accumulator is an important register associated with the ALU. The accumulator in 8051 is an 8 – bit register.

- 38. RAM: 8051 Microcontroller has 128 Bytes of RAM which includes SFRs and Input / Output Port Registers. ROM: 8051 has 4 KB of on-chip ROM (Program Memory). I/O Ports: 8051 has four 8 – bit Input / Output Ports which are bit addressable and bidirectional. Timers / Counters: 8051 has two 16 – bit Timers / Counters. Serial Port: 8051 supports full duplex UART Communication. External Memory: 8051Microcontroller can access two 16 – bit address line at once: one each for RAM and ROM. The total external memory that an 8051 Microcontroller can access for RAM and ROM is 64KB (216 for each type). Additional Features: Interrupts, on-chip oscillator, Boolean Processor, Power Down Mode, etc.

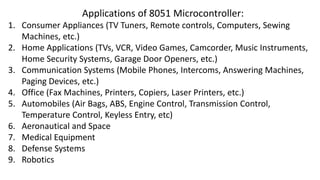

- 39. Applications of 8051 Microcontroller: 1. Consumer Appliances (TV Tuners, Remote controls, Computers, Sewing Machines, etc.) 2. Home Applications (TVs, VCR, Video Games, Camcorder, Music Instruments, Home Security Systems, Garage Door Openers, etc.) 3. Communication Systems (Mobile Phones, Intercoms, Answering Machines, Paging Devices, etc.) 4. Office (Fax Machines, Printers, Copiers, Laser Printers, etc.) 5. Automobiles (Air Bags, ABS, Engine Control, Transmission Control, Temperature Control, Keyless Entry, etc) 6. Aeronautical and Space 7. Medical Equipment 8. Defense Systems 9. Robotics

- 40. Core Processor: It is an individual processor within a CPU Shared-memory parallel Distributed-memory parallel with message passing between tasks Task-level parallelization

![Instruction-Level Parallelism:

• Parallelism is exploited within individual instructions to get more instructions/sec out of

the machine.

• We will consider two approached

– Pipelining

– Superscalar Architectures

A] Pipeline:

• Fetching of instructions from memory is a major bottleneck in instruction execution speed.

However, computers have the ability to fetch instructions from memory in advance

• These instructions were stored in a set of registers called the prefetch buffer.

• Thus, instruction execution is divided into two parts: fetching and actual execution;

• The concept of a pipeline carries this strategy much further.

• Instead of dividing instruction execution into only two parts, it is often divided into many

parts, each one handled by a dedicated piece of hardware, all of which can run in parallel.](https://image.slidesharecdn.com/unit6updated-210312101651/85/Computer-Organization-Introduction-to-Microprocessor-and-Microcontroller-28-320.jpg)

![B] Superscalar Architectures:

• Going to four pipelines is conceivable, but doing so duplicates too much

hardware

• Instead, a different approach is used on highend CPUs.

• The basic idea is to have just a single pipeline but give it multiple

functional units.

• This is a superscalar architecture – using more than one ALU, so that

more than one instruction can be executed in parallel.

• Implicit in the idea of a superscalar processor is that the S3 stage can

issue instructions considerably faster than the S4 stage is able to execute

them.](https://image.slidesharecdn.com/unit6updated-210312101651/85/Computer-Organization-Introduction-to-Microprocessor-and-Microcontroller-30-320.jpg)