Microprocessor and Microcontroller Lab Manual!

- 1. freshupdates.in SYLLABUS EE2356 - MICROPROCESSOR AND MICRO CONTROLLER LABORATORY AIM 1. To understand programming using instruction sets of processors. 2. To study various digital & linear 8-bit Microprocessor 1. Simple arithmetic operations: Multi precision addition / subtraction / multiplication / division. 2. Programming with control instructions: Increment / Decrement, Ascending / Descending order, Maximum / Minimum of numbers, Rotate instructions - Hex / ASCII / BCD code conversions. 3. Interface Experiments: • A/D Interfacing. • D/A Interfacing. • Traffic light controller. 4. Interface Experiments: Simple experiments using 8251, 8279, 8254. 8-bit Microcontroller 5. Demonstration of basic instructions with 8051 Micro controller execution, including: • Conditional jumps, looping • Calling subroutines. • Stack parameter testing 6. Parallel port programming with 8051 using port 1 facility: - Stepper motor and D / A converter. 7. Study of Basic Digital IC’s (Verification of truth table for AND, OR, EXOR, NOT, NOR, NAND, JK FF, RS FF,D FF) 8. Implementation of Boolean Functions, Adder / Subtractor circuits. 9. Combination Logic; Adder, Subtractor, Code converters, Encoder and Decoder 10. Sequential Logic; Study of Flip-Flop,Counters(synchronous and asynchronous),Shift Registers

- 2. freshupdates.in LIST OF EXPERIMENTS Ex. No Page No. 8 – BIT MICROPROCESSOR (8085) 1 1(a) 8- bit Addition 1(b) 8 – bit Subtraction 1(c) 8- bit Multiplication 1(d) 8- bit Division 2 2(a) Ascending order 2(b) Descending order 2( c) Largest of a given numbers 2(d) Smallest of a given numbers 3 3(a) Code Conversion: ASCII to Hexadecimal 3(b) Code Conversion: Hexadecimal to ASCII 3(c) Code Conversion: Hexadecimal to Binary 3(d) Code Conversion: Hexadecimal to BCD 4 4(a) Interfacing: ADC with 8085 4(b)Interfacing: DAC with 8085 5 Interfacing: Traffic Light Controller with 8085 6 6(a)Interfacing: 8251 with 8085 6(b) Interfacing: 8279 with 8085 6(c) Interfacing: 8253 with 8085 MICROCONTROLLER(8051) 7 7(a) Sum of elements in an array 7(b) Sum using Stack 7( c) Sum using call option 8 8(a) Interfacing: Stepper Motor with 8051 8(b) Interfacing: DAC with 8051 STUDY OF BASIC DIGITAL IC’S 9 Verification of truth table for AND, OR, EXOR, NOT, NOR, NAND, JK FF, RS FF,D FF 10 Implementation of Boolean Functions, Adder / Subtractor circuits 11 Code converters, Encoder and Decoder 12 Study of Flipflops 13 Counters(synchronous and asynchronous), Shift registers 14 Differentiator, Integrator 15 Timer IC applications

- 5. freshupdates.in 2 Ex.No: 1 SIMPLE ARITHMETIC OPERATIONS AIM: To write an assembly language program to add, subtract, multiply and divide the given data stored at two consecutive locations using 8085 microprocessor. A. 8 BIT DATA ADDITION: ALGORITHM: 1. Initialize memory pointer to data location. 2. Get the first number from memory in accumulator. 3. Get the second number and add it to the accumulator. 4. Store the answer at another memory location.

- 6. freshupdates.in 3 FLOW CHART: NO YES START [HL] 4500H [A] [M] [A] [A]+[M] [HL] [HL]+1 STOP [HL] [HL]+1 [M] [A] [C] 00H [M] [C] [HL] [HL]+1 Is there a Carry ? [C] [C]+1

- 7. freshupdates.in 4 PROGRAM: ADDRESS OPCODE LABEL MNEMONICS OPERAND COMMENT 4100 START MVI C, 00 Clear C reg. 4101 4102 LXI H, 4500 Initialize HL reg. to 45004103 4104 4105 MOV A, M Transfer first data to accumulator 4106 INX H Increment HL reg. to point next memory Location. 4107 ADD M Add first number to acc. Content. 4108 JNC L1 Jump to location if result does not yield carry. 4109 410A 410B INR C Increment C reg. 410C L1 INX H Increment HL reg. to point next memory Location. 410D MOV M, A Transfer the result from acc. to memory. 410E INX H Increment HL reg. to point next memory Location. 410F MOV M, C Move carry to memory 4110 HLT Stop the program

- 8. freshupdates.in 5 B. 8 BIT DATA SUBTRACTION ALGORITHM: 1. Initialize memory pointer to data location. 2. Get the first number from memory in accumulator. 3. Get the second number and subtract from the accumulator. 4. If the result yields a borrow, the content of the acc. is complemented and 01H is added to it (2’s complement). A register is cleared and the content of that reg. is incremented in case there is a borrow. If there is no borrow the content of the acc. is directly taken as the result. 5. Store the answer at next memory location.

- 9. freshupdates.in 6 FLOW CHART: NO YES START [HL] 4500H [A] [M] Is there a Borrow ? [A] [A]-[M] [HL] [HL]+1 [C] 00H [C] [C]+1 STOP [HL] [HL]+1 [M] [A] [M] [C] [HL] [HL]+1 Complement [A] Add 01H to [A]

- 10. freshupdates.in 7 PROGRAM: ADDRESS OPCODE LABEL MNEMONICS OPERAND COMMENT 4100 START MVI C, 00 Clear C reg. 4101 4102 LXI H, 4500 Initialize HL reg. to 45004103 4104 4105 MOV A, M Transfer first data to accumulator 4106 INX H Increment HL reg. to point next mem. Location. 4107 SUB M Subtract first number from acc. Content. 4108 JNC L1 Jump to location if result does not yield borrow. 4109 410A 410B INR C Increment C reg. 410C CMA Complement the Acc. content 410D ADI 01H Add 01H to content of acc.410E 410F L1 INX H Increment HL reg. to point next mem. Location. 4110 MOV M, A Transfer the result from acc. to memory. 4111 INX H Increment HL reg. to point next mem. Location. 4112 MOV M, C Move carry to mem. 4113 HLT Stop the program

- 11. freshupdates.in 8 C. 8 BIT DATA MULTIPLICATION: ALGORITHM: LOGIC: Multiplication can be done by repeated addition. 1. Initialize memory pointer to data location. 2. Move multiplicand to a register. 3. Move the multiplier to another register. 4. Clear the accumulator. 5. Add multiplicand to accumulator 6. Decrement multiplier 7. Repeat step 5 till multiplier comes to zero. 8. The result, which is in the accumulator, is stored in a memory location.

- 12. freshupdates.in 9 FLOW CHART: NO YES NO YES [HL] 4500 B M A 00 C 00 Is there any carry C C+1 B B-1 [A] [A] +[M] [HL] [HL]+1 IS B=0 A START

- 13. freshupdates.in 10 A STOP [HL] [HL]+1 [M] [A] [M] [C] [HL] [HL]+1

- 14. freshupdates.in 11 PROGRAM: ADDRESS OPCODE LABEL MNEMONICS OPERAND COMMENT 4100 START LXI H, 4500 Initialize HL reg. to 4500 Transfer first data to reg. B 4101 4102 4103 MOV B, M 4104 INX H Increment HL reg. to point next mem. Location. 4105 MVI A, 00H Clear the acc. 4106 4107 MVI C, 00H Clear C reg for carry 4108 4109 L1 ADD M Add multiplicand multiplier times. 410A JNC NEXT Jump to NEXT if there is no carry410B 410C 410D INR C Increment C reg 410E NEXT DCR B Decrement B reg 410F JNZ L1 Jump to L1 if B is not zero.4110 4111 4112 INX H Increment HL reg. to point next mem. Location. 4113 MOV M, A Transfer the result from acc. to memory. 4114 INX H Increment HL reg. to point next mem. Location. 4115 MOV M, C Transfer the result from C reg. to memory. 4116 HLT Stop the program

- 15. freshupdates.in 12 D. 8 BIT DIVISION: ALGORITHM: LOGIC: Division is done using the method Repeated subtraction. 1. Load Divisor and Dividend 2. Subtract divisor from dividend 3. Count the number of times of subtraction which equals the quotient 4. Stop subtraction when the dividend is less than the divisor .The dividend now becomes the remainder. Otherwise go to step 2. 5. stop the program execution.

- 16. freshupdates.in 13 FLOWCHART: NO YES B 00 M A-M [B] [B] +1 IS A<0 A A+ M B B-1 [HL] 4500 A M [HL] [HL]+1 START STOP [HL] [HL]+1 [M] [A] [M] [B] [HL] [HL]+1

- 17. freshupdates.in 14 PROGRAM: ADDRESS OPCODE LABEL MNEMONICS OPERAND COMMENTS 4100 MVI B,00 Clear B reg for quotient 4101 4102 LXI H,4500 Initialize HL reg. to 4500H4103 4104 4105 MOV A,M Transfer dividend to acc. 4106 INX H Increment HL reg. to point next mem. Location. 4107 LOOP SUB M Subtract divisor from dividend 4108 INR B Increment B reg 4109 JNC LOOP Jump to LOOP if result does not yield borrow 410A 410B 410C ADD M Add divisor to acc. 410D DCR B Decrement B reg 410E INX H Increment HL reg. to point next mem. Location. 410F MOV M,A Transfer the remainder from acc. to memory. 4110 INX H Increment HL reg. to point next mem. Location. 4111 MOV M,B Transfer the quotient from B reg. to memory. 4112 HLT Stop the program OBSERVATION:

- 18. freshupdates.in 15 ADDITION: S.NO INPUT OUTPUT ADDRESS DATA ADDRESS DATA 1 4500 4502 4501 4503 2 4500 4502 4501 4503 SUBTRACTION: S.NO INPUT OUTPUT ADDRESS DATA ADDRESS DATA 1 4500 4502 4501 4503 2 4500 4502 4501 4503 MULTIPLICATION: S.NO INPUT OUTPUT ADDRESS DATA ADDRESS DATA 1 4500 4502 4501 4503 2 4500 4502 4501 4503 DIVISION: S.NO INPUT OUTPUT ADDRESS DATA ADDRESS DATA 1 4500 4502 4501 4503 2 4500 4502 4501 4503

- 19. freshupdates.in 16 RESULT: Thus the addition, subtraction, multiplication and division of two numbers was performed using the 8085 microprocessor.

- 20. freshupdates.in 17 Ex.No: 2 SORTING OF AN ARRAY AIM: To write an assembly language program to arrange an array of data in ascending and descending order and to find the smallest and largest data among the array. A. ASCENDING ORDER ALGORITHM: 1. Get the numbers to be sorted from the memory locations. 2. Compare the first two numbers and if the first number is larger than second then I interchange the number. 3. If the first number is smaller, go to step 4 4. Repeat steps 2 and 3 until the numbers are in required order

- 21. freshupdates.in 18 FLOWCHART: YES NO [B] 04H [HL] [8100H] [A] [HL] [HL [HL] + 1 IS [A] < [HL]? [D] [HL] [HL] [A] [HL] [HL] - 1 [HL] [D] [HL] [HL] + 1 [C] [C] – 01 H A [C] 04H START

- 22. freshupdates.in 19 NO YES NO YES IS [C] = 0? A [B] [B]-1 IS [B] = 0? STOP

- 23. freshupdates.in 20 PROGRAM: ADDRESS OPC ODE LABEL MNEMONICS OPERA ND COMMENTS 4100 MVI B,04 Initialize B reg with number of comparisons (n-1) 4101 4102 LOOP 3 LXI H,4200 Initialize HL reg. to 4200H4103 4104 4105 MVI C,04 Initialize C reg with no. of comparisons(n-1)4106 4107 LOOP2 MOV A,M Transfer first data to acc. 4108 INX H Increment HL reg. to point next memory location 4109 CMP M Compare M & A 410A JC LOOP1 If A is less than M then go to loop1410B 410C 410D MOV D,M Transfer data from M to D reg 410E MOV M,A Transfer data from acc to M 410F DCX H Decrement HL pair 4110 MOV M,D Transfer data from D to M 4111 INX H Increment HL pair 4112 LOOP1 DCR C Decrement C reg 4113 JNZ LOOP2 If C is not zero go to loop24114 4115 4116 DCR B Decrement B reg 4117 JNZ LOOP3 If B is not Zero go to loop34118 4119 411A HLT Stop the program

- 24. freshupdates.in 21 B. DESCENDING ORDER ALGORITHM: 1. Get the numbers to be sorted from the memory locations. 2. Compare the first two numbers and if the first number is smaller than second then I interchange the number. 3. If the first number is larger, go to step 4 4. Repeat steps 2 and 3 until the numbers are in required order

- 25. freshupdates.in 22 FLOWCHART: NO YES [B] 04H [HL] [8100H] [A] [HL] [HL [HL] + 1 IS [A] < [HL]? [D] [HL] [HL] [A] [HL] [HL] - 1 [HL] [D] [HL] [HL] + 1 [C] [C] – 01 H A [C] 04H START

- 26. freshupdates.in 23 NO YES NO YES IS [C] = 0? A [B] [B]-1 IS [B] = 0? STOP

- 27. freshupdates.in 24 PROGRAM: ADDRE SS OPCO DE LABEL MNEM ONICS OPER AND COMMENTS 4100 MVI B,04 Initialize B reg with number of comparisons (n-1)4101 4102 LOOP 3 LXI H,4200 Initialize HL reg. to 4200H4103 4104 4105 MVI C,04 Initialize C reg with no. of comparisons(n-1)4106 4107 LOOP2 MOV A,M Transfer first data to acc. 4108 INX H Increment HL reg. to point next memory location 4109 CMP M Compare M & A 410A JNC LOOP1 If A is greater than M then go to loop1410B 410C 410D MOV D,M Transfer data from M to D reg 410E MOV M,A Transfer data from acc to M 410F DCX H Decrement HL pair 4110 MOV M,D Transfer data from D to M 4111 INX H Increment HL pair 4112 LOOP1 DCR C Decrement C reg 4113 JNZ LOOP2 If C is not zero go to loop2 4114 4115 4116 DCR B Decrement B reg 4117 JNZ LOOP3 If B is not Zero go to loop3 4118 4119 411A HLT Stop the program

- 28. freshupdates.in 25 C. LARGEST ELEMENT IN AN ARRAY ALGORITHM: 1. Place all the elements of an array in the consecutive memory locations. 2. Fetch the first element from the memory location and load it in the accumulator. 3. Initialize a counter (register) with the total number of elements in an array. 4. Decrement the counter by 1. 5. Increment the memory pointer to point to the next element. 6. Compare the accumulator content with the memory content (next element). 7. If the accumulator content is smaller, then move the memory content (largest element) to the accumulator. Else continue. 8. Decrement the counter by 1. 9. Repeat steps 5 to 8 until the counter reaches zero 10. Store the result (accumulator content) in the specified memory location.

- 29. freshupdates.in 26 FLOW CHART: NO YES NO YES [B] 04H [HL] [8100H] [A] [HL] [HL [HL] + 1 IS [A] < [HL]? [A] [HL] [8105] [A] START [B] [B]-1 IS [B] = 0? STOP

- 30. freshupdates.in 27 PROGRAM: ADDRE SS OPCO DE LABEL MNEM ONICS OPER AND COMMENTS 4101 LXI H,4200 Initialize HL reg. to 4200H4102 4103 4104 MVI B,04 Initialize B reg with no. of comparisons(n-1)4105 4106 MOV A,M Transfer first data to acc. 4107 LOOP1 INX H Increment HL reg. to point next memory location 4108 CMP M Compare M & A 4109 JNC LOOP If A is greater than M then go to loop410A 410B 410C MOV A,M Transfer data from M to A reg 410D LOOP DCR B Decrement B reg 410E JNZ LOOP1 If B is not Zero go to loop1 410F 4110 4111 STA 4205 Store the result in a memory location.4112 4113 4114 HLT Stop the program

- 31. freshupdates.in 28 D.SMALLEST ELEMENT IN AN ARRAY ALGORITHM: 1. Place all the elements of an array in the consecutive memory locations. 2. Fetch the first element from the memory location and load it in the accumulator. 3. Initialize a counter (register) with the total number of elements in an array. 4. Decrement the counter by 1. 5. Increment the memory pointer to point to the next element. 6. Compare the accumulator content with the memory content (next element). 7. If the accumulator content is smaller, then move the memory content (largest element) to the accumulator. Else continue. 8. Decrement the counter by 1. 9. Repeat steps 5 to 8 until the counter reaches zero 10. Store the result (accumulator content) in the specified memory location.

- 32. freshupdates.in 29 FLOW CHART: YES NO NO YES [B] 04H [HL] [8100H] [A] [HL] [HL [HL] + 1 IS [A] < [HL]? [A] [HL] [8105] [A] START [B] [B]-1 IS [B] = 0? STOP

- 33. freshupdates.in 30 PROGRAM: ADDRE SS OPCO DE LABEL MNEM ONICS OPER AND COMMENTS 4101 LXI H,4200 Initialize HL reg. to 4200H4102 4103 4104 MVI B,04 Initialize B reg with no. of comparisons(n-1)4105 4106 MOV A,M Transfer first data to acc. 4107 LOOP1 INX H Increment HL reg. to point next memory location 4108 CMP M Compare M & A 4109 JC LOOP If A is lesser than M then go to loop410A 410B 410C MOV A,M Transfer data from M to A reg 410D LOOP DCR B Decrement B reg 410E JNZ LOOP1 If B is not Zero go to loop1 410F 4110 4111 STA 4205 Store the result in a memory location.4112 4113 4114 HLT Stop the program

- 34. freshupdates.in 31 OBSERVATION: A. ASCENDING ORDER INPUT OUTPUT MEMORY LOCATION DATA MEMORY LOCATION DATA 4200 4200 4201 4201 4202 4202 4203 4203 4204 4204 B. DESCENDING ORDER INPUT OUTPUT MEMORY LOCATION DATA MEMORY LOCATION DATA 4200 4200 4201 4201 4202 4202 4203 4203 4204 4204 C. SMALLEST ELEMENT INPUT OUTPUT MEMORY LOCATION DATA MEMORY LOCATION DATA 4200 4201 4202 4205 4203 4204 D. LARGEST ELEMENT INPUT OUTPUT MEMORY LOCATION DATA MEMORY LOCATION DATA 4200 4201 4202 4205 4203 4204

- 35. freshupdates.in 32 RESULT: Thus the sorting operations of arranging an array in ascending, descending order and the largest and smallest element were found using the 8085 microprocessor.

- 36. freshupdates.in 33 Ex.No: 3 CODE CONVERSIONS AIM: To write an assembly language program to perform the conversions of ASCII to hexadecimal number, hexadecimal to ASCII, hexadecimal to decimal number, binary to hexadecimal number and hexadecimal to binary number. A.ASCII TO HEXADECIMAL ALGORITHM: 1. Start the program 2. Load the data from address 4200 to A 3. Move data from accumulator to C 4. Move data from M to HL pair to accumulator 5. Subtract the data 30 from A 6. Decrement content of register 7. Stop the program if C is zero 8. Jump to Step 5 9. End the program

- 37. freshupdates.in 34 FLOWCHART: YES NO Start Set the ASCII value Check for Carry? Decrement the register content Subtract 30 from A Subtract 07 from A Store the hex value Stop

- 38. freshupdates.in 35 PROGRAM: ADDRE SS OPCO DE LABEL MNEM ONICS OPER AND COMMENTS 4100 LDA H,4200 Load data 4200 to A 4101 4102 4103 MOV C,A 4F Move data from A to C 4104 LXI H,4201 Load address 4201 in HL 4105 4106 4107 LXI D,4301 Load address 4301 in DF 4108 4109 410A LOOP 1 MOV A,M Move data from M to A 410B SUI 30 Subtract 30 from A 410C 410D STAX D Store data from accumulator to DE 410E DCR C Decrement from C register 410F JZ LOOP Stop program if C is 0 4110 4111 4112 INX H Increment HL register pair 4113 INX D Increment DE register pair 4114 JMP LOOP 1 Jump to 410A 4115 4116 4117 LOOP HLT Stop

- 39. freshupdates.in 36 B. HEXADECIMAL TO ASCII ALGORITHM: 1. Start the program 2. Load the data from address 4200 to A 3. Move data from accumulator to C 4. Move data from M to HL pair to accumulator 5. Add the data 30 to A 6. Decrement content of register 7. Stop the program if C is zero 8. Jump to Step 5 9. End the program

- 40. freshupdates.in 37 FLOWCHART: YES NO Set the ASCII value Check for Carry? Decrement the register content Add 30 to A Store the decimal value Stop Start

- 41. freshupdates.in 38 PROGRAM: ADDRE SS OPCO DE LABEL MNEM ONICS OPER AND COMMENTS 4100 LDA H,4200 Load data 4200 to A 4101 4102 4103 MOV C,A 4F Move data from A to C 4104 LXI H,4201 Load address 4201 in HL 4105 4106 4107 LXI D,4301 Load address 4301 in DF 4108 4109 410A LOOP 1 MOV A,M Move data from M to A 410B ADI 30 Subtract 30 from A 410C 410D STAX D Store data from accumulator to DE 410E DCR C Decrement from C register 410F JZ LOOP Stop program if C is 0 4110 4111 4112 INX H Increment HL register pair 4113 INX D Increment DE register pair 4114 JMP LOOP 1 Jump to 410A 4115 4116 4117 LOOP HLT Stop

- 42. freshupdates.in 39 C. HEXADECIMAL TO BINARY ALGORITHM: 1. Start the program 2. Move the content of memory to accumulator 3. Move data 0B o register B 4. Increment the content of HL register pair 5. Rotate the accumulator right 6. Jump to the specified address if carry generated 7. Move 00 to memory 8. Jump to specified address if there is no zero 9. Move 01 to memory 10. Jump to specified address if there is no zero 11. End the program

- 43. freshupdates.in 40 FLOWCHART: YES NO NO YES Load address in HL pair Check for Carry? Initialize counter B to 08 Move data from M to A Stop Start Increment HL register pair Rotate accumulator right Decrement B register Move data from 01 to M Move data from 00 to M If B=0?

- 44. freshupdates.in 41 PROGRAM: ADDRE SS OPCO DE LABEL MNEM ONICS OPERAND COMMENTS 4100 LXI H,4200 Load address in HL pair 4101 4102 4103 MOV A,M Move content of M to A 4104 MVI B 08 Move 0B to register pair 4105 4106 L3 INX H Increment the content of HL pair 4107 RRC Rotate accumulator right 4108 JC L1 Jump to specified address if carry 4109 410A 410B MVI M 00 Move 00 to M 410C JMP L2 Decrement B register 410D 410E 410F L1 MVI M 01 Move 01 to M 4110 4111 L2 DCR B Decrement B by 1 4112 JNZ L3 Jump to the specified address if no zero 4113 4114 4115 HLT Stop the program

- 45. freshupdates.in 42 D. BINARY TO HEXADECIMAL ALGORITHM: 1. Start the program 2. Load the address in HL pair 3. Move the content of memory to accumulator 4. Add the content of accumulator with previous content of accumulator 5. Move the content of B to accumulator 6. Add the content of accumulator with previous content of accumulator 7. Repeat step 6 8. Add B with accumulator content 9. Increment H by 1 10. Move content of M to A 11. End the program

- 46. freshupdates.in 43 FLOWCHART: Load address in HL pair Add content of A to register B Move data from M to A Start Add content of A with itself Add content of A to register B Increment HL reg pair content Add content of M with accumulator Increment HL reg pair Move content of M to accumulator Stop

- 47. freshupdates.in 44 PROGRAM: ADDRE SS OPCO DE LABEL MNEM ONICS OPERAND COMMENTS 4100 LXI H,4150 Load address in HL pair 4101 4102 4103 MOV M,A Move content of A to M 4104 ADD A Add A content with previous content of A 4105 MOV B,A Move the content from A to B 4106 ADD A Add A content with previous content of A 4107 ADD B Add B content with A 4108 INX H Increment H by 1 4109 ADD M Add M content with A 410A INX H Increment H by 1 410B MOV M,A Move content of A to M 410C HLT Stop the program

- 48. freshupdates.in 45 E. HEXADECIMAL TO DECIMAL ALGORITHM: 1. Start the program 2. Load the address in HL pair 3. Move the content from HL to A 4. Subtract 64 from A 5. Increment BC pair 6. Jump to address 4207 7. Subtract 0A from A 8. Increment HL pair 9. Rotate accumulator left 10. Increment HL pair 11. End the program

- 49. freshupdates.in 46 FLOWCHART: YES NO NO YES Load address in HL pair Check Carry? Clear accumulator Initialize D register Stop Start Move HL to C register Add 01 with A Store A in 4150 H Move D to accumulator Store A in 4151 H Adjust A to BCD Increment C register Increment D register Check Carry?

- 50. freshupdates.in 47 PROGRAM: ADDRE SS OPCO DE LABEL MNEM ONICS OPER AND COMMENTS 4100 LXI H 4150 Load data from 4150 to HL pair 4101 4102 LXI B 0000 Load data from address to BC 4103 4104 4105 4106 MOV A,M Move the content from HL to A 4107 L4 SUI 64 Subtract 64 from A 4108 4109 JC L1 Stop if A has carry 410A 410B 410C INR B Increment BC 410D JMP L4 Jump to specified address 410E 410F 4110 L1 ADI 64 Add 64 to A 4111 4112 L3 SUI 0A Subtract 0A from A 4113 4114 JC L2 Stop if A has carry 4115 4116 4117 INR C Increment HL 4118 L2 JNC L3 Stop if A has no carry 4119 411A 411B ADI 0A Add 0A to A 411D INX H Increment HL 411E MOV M,B Move B to M 411F MOV B,A Move A to B 4120 MOV A,B Move B to A 4121 RLC Rotate accumulator 4122 RLC Rotate accumulator 4123 RLC Rotate accumulator 4124 RLC Rotate accumulator 4125 ADD B Add B to A 4126 INX H Increment H by 1 4127 MOV M,A Move content of A to M 4128 HLT Stop the program

- 51. freshupdates.in 48 OBSERVATION: A. ASCII TO HEXADECIMAL INPUT OUTPUT MEMORY LOCATION DATA MEMORY LOCATION DATA 4201 4301 B. HEXADECIMAL TO ASCII INPUT OUTPUT MEMORY LOCATION DATA MEMORY LOCATION DATA 4201 4301 C. HEXADECIMAL TO BINARY INPUT OUTPUT MEMORY LOCATION DATA MEMORY LOCATION DATA MEMORY LOCATION DATA 4200 4200 4204 4201 4205 4202 4206 4203 4207 D. BINARY TO HEXADECIMAL INPUT OUTPUT MEMORY LOCATION DATA MEMORY LOCATION DATA 4150 41524151 E. HEXADECIMAL TO DECIMAL INPUT OUTPUT MEMORY LOCATION DATA MEMORY LOCATION DATA 4150 41524151

- 52. freshupdates.in 49 RESULT: Thus the assembly language programs for various code conversions are executed using 8085 microprocessor.

- 53. freshupdates.in 50 EX.No:4 4(a) INTERFACING A/D AND D/A CONVERTER WITH 8085 AIM: To write an assembly language program to convert an analog signal into a digital signal and a digital signal into an analog signal using an ADC interfacing and DAC interfacing respectively. A. ADC INTERFACING WITH 8085 APPARATUS REQUIRED: SL.NO ITEM SPECIFICATION QUANTITY 1 Microprocessor kit 8085,Vi Microsystems 1 2 Power supply +5 V dc 1 3 ADC Interface board Vi Microsystems 1 PROBLEM STATEMENT: To program starts from memory location 4100H. The program is executed for various values of analog voltage which are set with the help of a potentiometer. The LED display is verified with the digital value that is stored in the memory location 4150H. THEORY: An ADC usually has two additional control lines: the SOC input to tell the ADC when to start the conversion and the EOC output to announce when the conversion is complete. The following program initiates the conversion process, checks the EOC pin of ADC 0419 as to whether the conversion is over and then inputs the data to the processor. It also instructs the processor to store the converted digital data at RAM 4200H. ALGORITHM: 1. Select the channel and latch the address. 2. Send the start conversion pulse. 3. Read EOC signal. 4. If EOC =1 continue else go to step (3) 5. Read the digital output. 6. Store it in a memory location.

- 54. freshupdates.in 51 PROGRAM: ADDRESS LABEL MNEMON ICS OPCO DE OPERA ND COMMENTS 4100 MVI A 10 Select channel 0 and to make accumulator low 4101 4102 OUT 0C8HC8 Output the data 4103 4104 MVI A A, 1818 Make accumulator high 4105 4106 OUT 0C8HC8 Display the data 4107 4108 MVI A 01 Make 01 to accumulator 4109 410A OUT 0D0HD0 Display the data 410B 410C XRA A XOR with accumulator 410D XRA A XOR with accumulator 410E XRA A XOR with accumulator 410F MVI A 00 Make 00 to accumulator 4110 4111 OUT D0 Load D0 in output port 4112 4113 LOOP IN D8 4114 4115 ANI 01 01 Do and operation directly 4116 4117 CPI 01 01 Compare with accumulator 4118 4119 JNZ LOOP Jump to specified address 411A 411B 411C IN C0 411D 411E STA 4150 Store the data 411F 4120 4121 HLT End the program

- 55. freshupdates.in 52 ADC- CIRCUIT: SOC JUMPER SELECTION: J2 : SOC Jumper selection J5 : Channel selection

- 56. freshupdates.in 53 OBSERVATION ANALOG VOLTAGE DIGITAL DATA ON LED DISPLAY HEX CODE IN LOCATION 4150

- 57. freshupdates.in 54 4(b) DAC INTERFACING WITH 8085 APPARATUS REQUIRED: SL.NO ITEM SPECIFICATION QUANTITY 1 Microprocessor kit 8085,Vi Microsystems 1 2 Power supply +5 V dc 1 3 DAC Interface board Vi Microsystems 1 SOFTWARE EXAMPLES The following examples illustrate how to control the DAC using 8085 and generate sine wave, saw tooth wave by means of software. (a) SQUARE WAVE GENERATION: The basic idea behind the generation of waveforms is the continuous generation of Analog output of DAC. With 00(HEX) as input to DAC2, the analog output is -5V. Similarly, with FF (Hex) as input, the output is +5V. Outputting digital data 00 and FF at regular intervals, to DAC2, results in a square wave of amplitude I5 Volts ALGORITHM: 1. Load the initial value (00) to Accumulator and move it to DAC. 2. Call the delay program 3. Load the final value (FF) to accumulator and move it to DAC. 4. Call the delay program. 5. Repeat steps 2 to 5. PROGRAM: ADDRESS LABEL MNEMON ICS OPC ODE OPERAND COMMENT 4100 START MVI A 00 Move 00 to A register 4101 4102 OUT C8 Load C8 to output port 4103 4104 CALL DELAY DELAY Call delay program 4107 MVI A FF Load FF to B register 4109 OUT C8 410B CALL DELAY DELAY 410E JMP START START Jump to start of address 4112 DELAY MVI B 05 Move 05 to B register 4114 L1 MVI C FF Move FF to C register

- 58. freshupdates.in 55 4116 L2 DCR C Decrement C 4117 JNZ L2 L2 Jump to L2 if no zero 411A DCR B Decrement B register 411B JNZ L1 L1 Jump to L1 if no zero 411E RET Execute the program and using a CRO, verify that the waveform at the DAC2 output is a square-wave. Modify the frequency of the square-wave, by varying the time delay. (b) SAW TOOTH GENERATION: ALGORITHM: 1. Load the initial value (00) to Accumulator 2. Move the accumulator content to DAC. 3. Increment the accumulator content by 1. 4. Repeat steps 3 and 4. Output digital data from 00 to FF constant steps of 01 to DAC1 repeat this sequence again and again. As a result a saw – tooth wave will be generated at DAC1 output. PROGRAM: ADDRESS LABEL MNEMON ICS OPCO DE OPERAN D COMMENT 4100 START MVI A 00 Load 00 to accumulator 4102 L1 OUT C0 Load CO in output port 4104 INR A Increment A register 4105 JNZ L1 L1 Jump to L1 if no zero 4108 JMP START START Go to START unconditionally (c) TRIANGULAR WAVE GENERATION: ALGORITHM: 1. Load the initial value (00) to Accumulator. 2. Move the accumulator content to DAC 3. Increment the accumulator content by 1. 4. If accumulator content is zero proceed to next step. Else go to step 3. 5. Load value (FF) to accumulator. 6. Move the accumulator content to DAC. 7. Decrement the accumulator content by 1. 8. If accumulator content is zero go to step 2. Else go to step 2. The following program will generate a triangular wave at DAC2 output.

- 59. freshupdates.in 56 PROGRAM: ADDRESS LABEL MNEMON ICS OPC ODE OPERA ND COMMENT START MVI L 00 Move 00 to L register L1 MOV A,L Load L to a register OUT C8 Load c8 to output port INR L Increment L register JNZ L1 L1 Jump to L1 if no zero MVI L FF Load FF to L register L2 MOV A,L Move L to a register OUT C8 Load C8 to output port DCR L Decrement L register JNZ L2 L2 Jump to L2 if no zero JMP START START Go to START unconditionally

- 61. freshupdates.in 58 OBSERVATION: WAVE FORMS AMPLITUDE TIME PERIOD Square waveform Saw tooth waveform Triangular waveform Result: Thus the conversion of an analog signal into a digital signal and a digital signal into an analog signal was done using interfacing of ADC and DAC respectively with 8085.

- 62. freshupdates.in 59 EX.No:5 TRAFFIC LIGHT CONTROLLER WITH 8085 AIM To write an assembly language program to simulate the traffic light at an intersection using a traffic light interface. APPARATUS REQUIRED: SL.NO ITEM SPECIFICATION QUANTITY 1 Microprocessor kit 4185,Vi Microsystems 1 2 Power supply +5 V dc 1 3 Traffic light interface kit Vi Microsystems 1 ALGORITHM: 1. Initialize the ports. 2. Initialize the memory content, with some address to the data. 3. Read data for each sequence from the memory and display it through the ports. 4. After completing all the sequences, repeat from step2. A SAMPLE SEQUENCE: 1. (a) Vehicles from south can go to straight or left. (b) Vehicles from west can cross the road. (c) Each pedestrian can cross the road. (d) Vehicles from east no movement. (e) Vehicles from north, can go only straight. 2. All ambers are ON, indicating the change of sequence. 3. (a) Vehicles from east can go straight and left. (b) Vehicles from south, can go only left. (c) North pedestrian can cross the road. (d) Vehicles from north, no movement. (e) Vehicles from west, can go only straight. 4. All ambers are ON, indicating the change of sequence. 5. (a) Vehicles from north can go straight and left. (b) Vehicles from east, can go only left. (c) West pedestrian can cross the road. (d) Vehicles from west, no movement. (e) Vehicles from south, can go only straight. 6. All ambers are ON, indicating the change of sequence.

- 63. freshupdates.in 60 7. (a) Vehicles from west can go straight and left. (b) Vehicles from north, can go only left. (c) South pedestrian can cross the road. (d) Vehicles from south, no movement. (e) Vehicles from east, can go only straight. 8. All ambers are ON, indicating the change of sequence. 9. (a) All vehicles from all directions no movement. (b) All pedestrian can cross the road. BIT ALLOCATION: BIT LED BIT LED BIT LED PA0 SOUTH LEFT PB0 NORTH LEFT PC0 WEST STRAIGHT PA1 SOUTH RIGHT PB1 NORTH RIGHT PC1 NORTH STRAIGHT PA2 SOUTH AMBER PB2 NORTH AMBER PC2 EAST STRAIGHT PA3 SOUTH RED PB3 NORTH RED PC3 SOUTH STRAIGHT PA4 EAST LEFT PB4 WEST LEFT PC4 NORTH PD PA5 EAST RIGHT PB5 WEST RIGHT PC5 WEST PD PA6 EAST AMBER PB6 WEST AMBER PC6 SOUTH PD PA7 EAST RED PB7 WEST RED PC7 EAST PD

- 64. freshupdates.in 61 PATH REPRESENTATION: CONTROL ----- 0F ( FOR 8255 PPI ) PORT A ----- 0C PORT B ----- 0D PORT C ----- 0E

- 65. freshupdates.in 62 PROGRAM : ADDRESS LABEL MNEMON ICS OPCO DE OPER AND COMMENT 4100 MVI A, 41 3E 41 Move 80 immediately to accumulator A,41 A,41 4102 OUT CONTROL D3 0F Output contents of accumulator to OF port 4104 LXI H,DATA_SQ Load address 417B to HL register 4107 LXI D,DATA_E 11 41,87 Load address 4187 to DE register 410A CALL OUT CD 42,41 Call out address 410D XCHG EB Exchange contents of HL with DE pair 410E MOV A,M 7E Move M content to accumulator 410F OUT PORT A D3 0C Load port A into output port 4111 CALL DELAY1 CD 66,41 Call delay address 4114 XCHG EB Exchange content of HL with DE pair 4115 INX D 13 Increment the content of D 4116 INX H 23 Increment the content of H 4117 CALL OUT CD 42,41 Call out the address 411A XCHG EB Exchange content of HL with DE pair 411B MOV A,M 7E Move M content to accumulator 411C OUT PORT B D3 0D Load port B into output port 411E CALL DELAY1 CD 66,41 Call DELAY address 4121 XCHG EB Exchange content of HL with DE pair 4122 INX D 13 Increment D register 4123 INX H 23 Increment H register 4124 CALL OUT CD 42,41 Call specified address 4127 XCHG EB Exchange content of HL with DE pair 4128 MOV A,M 7E Move M content to accumulator

- 66. freshupdates.in 63 4129 OUT PORT C D3 0E Load port C into output port 412B CALL DELAY1 CD 66,41 Call DELAY address 412E XCHG EB Exchange content of HL with DE pair 412F INX D 13 Increment D register 4130 INX H 23 Increment H register 4131 CALL OUT CD 42,41 Call specified address 4134 XCHG EB Exchange content of HL with DE pair 4135 MOV A,M 7E Move M content to accumulator 4136 OUT PORT C D3 0E Load port C into output port 4138 INX H 23 Increment H register 4139 MOV A,M 7E Move M content to accumulator 413A OUT PORT A D3 0C Load port A into output port 413C CALL DELAY1 CD 66,41 Call DELAY address 413F JMP REPEAT C3 04,41 Jump to specified address 4142 MOV A,M 7E Move M content to accumulator 4143 OUT PORT C D3 0E Load port C into output port 4145 INX H 23 Increment H register 4146 MOV A,M 7E Move M content to accumulator 4147 OUT PORT B D3 0D Load port B into output port 4149 INX H 23 Increment H register 414A MOV A,M 7E Move M content to accumulator 414B OUT PORT A D3 0C Load port A into output port 414D CALL DELAY CD 51,41 Call DELAY address 4150 RET C9 Return to accumulator 4151 PUSH H E5 Push the register H 4152 LXI H,001F 21 1F,00 Load 00 1F in HL register pair 4155 LXI B,FFFF 01 FF,FF Load FF FF in DE register pair 4158 DCX B 0B Decrement B register 4159 MOV A,B 78 Move B content to accumulator 415A ORA C B1 OR content of C with accumulator 415B JNZ LOOP C2 58,41 Jump to LOOP if no zero 415E DCX H 2B Decrement H register 415F MOV A,L 7D Move L content to accumulator

- 67. freshupdates.in 64 4160 ORA H B4 OR content of H with accumulator 4161 JNZ L1 C2 55,41 Jump to L1 if no zero 4164 POP H E1 Pop the register H 4165 RET C9 Return from subroutine 4166 PUSH H E5 Push the register H 4167 LXI H,001F 21 1F,00 Load 00 1F in HL register pair 416A LXI B,FFFF 01 FF,FF Load FF FF in DE register pair 416D DCX B 0B Decrement B register 416E MOV A,B 78 Move B content to accumulator 416F ORA C B1 OR content of C with accumulator 4170 JNZ LOOP2 C2 6D,41 Jump to LOOP2 if no zero 4173 DCX H 2B Decrement H register 4174 MOV A,L 7D Move L content to accumulator 4175 ORA H B4 OR content of H with accumulator 4176 JNZ L2 C2 6A,41 Jump to L2 if no zero 4179 POP H E1 Pop the register H 417A RET C9 Return to subroutine 417B DATA SEQ DB 12 27 44 10 2B 92 10 9D 84 48 2E 84 48 4B 20 49 04 RESULT: Thus an assembly language program to simulate the traffic light at an intersection using a traffic light interfaces was written and implemented.

- 68. freshupdates.in 65 EX.No:6 6(a) INTERFACING 8251 WITH 8085 AIM: To write a program to initiate 8251 and to check the transmission and reception of character. APPARATUS REQUIRED: 1. 8085 Microprocessor kit 2. 8251 Interface board 3. DC regulated power supply THEORY: The 8251 is used as a peripheral device for serial communication and is programmed by the CPU to operate using virtually any serial data transmission technique. The USART accepts data characters from the CPU in parallel format and the converts them in a continuous serial data stream of transmission. Simultaneously, it can receive serial data streams and convert them into parallel data characters for the CPU. The CPU can read the status of USART at any time. These include data transmissions errors and control signals. Prior to starting data transmission or reception ,the 8251 must be loaded with a set of control words generated by the CPU.These control signals define the complete functional definition of the 8251 and must immediately follow a RESET operation. Control words should be written in to the control register of 8251. words should be written in to the control register of 8251.words should be written in to the control register of 8251.Thesecontrol words are split into two formats. 1. MODE INSTRUCTION WORD 2. COMMAND INSTRUCTION WORD. 1. MODE INSTRUCTION WORD This format defines the BAUD rate, character length, parity and stop bits required to work with asynchronous data communication. by selecting the appropriate BAUD factor synchronous mode, the 8251 can be operated in synchronous mode. Initializing 8251 using the Mode instructions to the following conditions. 8 bit data No parity Baud rate factor(16X) 1 stop bit Gives a mode command word of 01001110=4E(X)

- 69. freshupdates.in 66 ALGORITHM 1. Initialize timer (8253) IC 2. Move the Mode command word (4EH) to A reg. 3. Output it port address C2 4. Move the command instruction word (37H) to A reg. 5. Output it to port address C2 6. Move the data to be transfer to A reg. 7. Output it to port address C0. 8. Reset the system 9. Get the data through input port address C0. 10. Store the value in memory 11. Reset the system PROGRAM: ADDRES S LA BE L MNEMON ICS OPC ODE OPE RAN D COMMENT 4100 MVI A 36 Move 36 to A 4102 OUT CE Output contents of accumulator to CE port 4104 MVI A 0A Move 0A to accumulator 4106 OUT C8 Output contents of accumulator to C8 port 4108 MVI A 00 Move 00 to accumulator 410A OUT C8 Output contents of accumulator to C8 port 410C LXI H 4200 Store 4200 address in HL register pair 410F MVI A 4E Move 4E to accumulator 4111 OUT C2 Output contents of accumulator to C2 port 4113 MVI A 37 Move 37 to accumulator 4115 OUT C2 Output contents of accumulator to C2 port 4117 MVI A 41 Move 41 to accumulator 4119 OUT C0 Output contents of accumulator to C0 port 411B RST1 4200 IN C0 Input the contents from port C0 to accumulator 4202 STA 4150 Store the output from accumulator to 4150 4205 RST1

- 70. freshupdates.in 67 SYNCHRONOUS MODE: S2 S1 EP PEN L2 L1 B2 B1 0 1 0 1 0 0 1 1 5 BIT 6 BIT 7 BIT 8 BIT EVEN PARITY GENERATION 0-Odd 1-Even PARITY ENABLE 1-Enable 0-Disable EXTERNAL SYNC DETECT 1-Sysdetect is an input 0- Sysdetect is an output SINGLE CHARACTER SYNC 1-Single sync character 0- Double sync character

- 71. freshupdates.in 68 ASYNCHRONOUS MODE: S2 S1 EP PEN L2 L1 B2 B1 0 1 0 1 0 0 1 1 Synch mode (1 X) (16 X) (64 X) 0 1 0 1 0 0 1 1 5 BIT 6 BIT 7 BIT 8 BIT 0 1 0 1 0 0 1 1 Invalid 61BIT 1.5BIT 2 BIT EVEN PARITY GENERATION 0-Odd 1-Even PARITY ENABLE 1-Enable 0-Disable

- 72. freshupdates.in 69 OBSERVATION: MEMORY LOCATION INPUT DATA OUTPUT DATA RESULT: Thus the program to initiate 8251 was written and the transmission and reception of character was checked by interfacing 8251 with 8085.

- 73. freshupdates.in 70 6(b) INTERFACING 8253 TIMER WITH 8085 AIM: To interface 8253 Interface board to 8085 microprocessor to demonstrate the generation of square wave. APPARATUS REQUIRED: 1. 8085 microprocessor kit 2. 8253 Interface board 3. DC regulated power supply 4. CRO. . PROGRAM: Address Opcodes Label Mnemonic Operands Comments 4100 3E 36 START: MVI A, 36 Channel 0 in mode 3 4102 D3 CE OUT CE Send Mode Control word 4104 3E 0A MVI A, 0A LSB of count 4106 D3 C8 OUT C8 Write count to register 4108 3E 00 MVI A, 00 MSB of count 410A D3 C8 OUT C8 Write count to register 410C 76 HLT Set the jumper, so that the clock 0 of 8253 is given a square wave of frequency 1.5 MHz. This program divides this PCLK by 10 and thus the output at channel 0 is 150 KHz. Vary the frequency by varying the count. Here the maximum count is FFFF H. So, the square wave will remain high for 7FFF H counts and remain low for 7FFF H counts. Thus with the input clock frequency of 1.5 MHz, which corresponds to a period of 0.067 microseconds, the resulting square wave has an ON time of 0.02184 microseconds and an OFF time of 0.02184 microseconds. To increase the time period of square wave, set the jumpers such that CLK2 of 8253 is connected to OUT 0. Using the above-mentioned program, output a square wave of frequency 150 KHz at channel 0. Now this is the clock to channel 2.

- 74. freshupdates.in 71 CONTROL WORD: SC1 SC2 RW1 RW0 M2 M1 M0 BCD SC-SELECT COUNTER: SC1 SC0 SELECT COUNTER 0 0 Select counter 0 0 1 Select counter 1 1 0 Select counter 2 1 1 Read back command M-MODE: M2 M1 M0 MODE 0 0 0 Mode 0 0 0 1 Mode 1 X 1 0 Mode 2 X 1 1 Mode 3 1 0 0 Mode 4 1 0 1 Mode 5 READ/WRITE: RW1 RW0 0 0 Counter latch command 0 1 R/W least significant bit only 1 0 R/W most significant bit only 1 1 R/W least sig first and most sig byte BCD: 0 Binary counter 16-bit 1 Binary coded decimal counter

- 75. freshupdates.in 72 Result: Thus the 8253 has been interfaced to 4185 p and six different modes of 8253 have been studied.

- 76. freshupdates.in 73 6(c) INTERFACING 8279 WITH 8085 AIM: To interface 8279 Programmable Keyboard Display Controller to 8085 Microprocessor. APPARATUS REQUIRED: 1. 8085 Microprocessor toolkit. 2. 8279 Interface board 3. Regulated D.C. power supply. PROGRAM: ADDRESS LABEL MNEMON ICS OPCO DE OPERA ND COMMENT 4100 START LXI H H, 4130H 4130 Store the 16 bit address in HL pair 4103 MVI D D, 0FH0F Move 0F to D register 4105 MVI A 10 Move 10 to A 4107 OUT C2 Output the contents of A to C2 output port C2H 4109 MVI A A, 90HCC Move CC to A 410B OUT C2 Output the contents of A to C2 output port 410D MVI A A, 90H90 Move 90 to A 410F OUT C2H C2 Output the contents of A to C2 output port 4111 LOOP MOV A, M Move content of M to A 4112 OUT C0HC0 Output the contents of M to A 4114 CALL DELAY DELAY DELAY Call the delay address 4117 INX H Increment H register 4118 DCR D D Decrement D register

- 77. freshupdates.in 74 4119 JNZ LOOP LOOP Jump to specified address 411C JMP START STARTSTART Jump to START address 411F DELAY MVI B A0 Move a to B register 4121 LOOP1 MVI C FF Move FF to C register 4123 LOOP2 DCR C Decrement C register 4124 JNZ LOOP 1 LOOP 1 Jump to LOOP 1 if no zero 4127 DCR B Decrement B register 4128 JNZ LOOP 2 LOOP 2 Jump to LOOP 2 if no zero 412B RET Pointer equal to 4130 .FF repeated eight times 4130 FF 4131 FF 4132 FF 4133 FF 4134 FF 4135 FF 4136 FF 4137 FF 4138 98 4139 68 413ª 7C 413B C8 413C 1C 413D 29 413E FF 413F FF

- 78. freshupdates.in 75 SEGMENT DEFINITION: DATA BUS D7 D6 D5 D4 D3 D2 D1 D0 SEGMETS d c b a dp g f e OBSERVATION: LETTER 7 SEGMENT DATA BUS HEXADECIMAL D7 D6 D5 D4 D3 D2 D1 D0 RESULT: Thus 8279 controller was interfaced with 8085 and program for rolling display was executed successfully.

- 80. freshupdates.in 77 Ex.No:7 7(a) 8051 - SUM OF ELEMENTS IN AN ARRAY AIM: To find the sum of elements in an array. ALGORITHM: 1. Load the array in the consecutive memory location and initialize the memory pointer with the starting address. 2. Load the total number of elements in a separate register as a counter. 3. Clear the accumulator. 4. Load the other register with the value of the memory pointer. 5. Add the register with the accumulator. 6. Check for carry, if exist, increment the carry register by 1. otherwise, continue 7. Decrement the counter and if it reaches 0, stop. Otherwise increment the memory pointer by 1 and go to step 4.

- 81. freshupdates.in 78 PROGRAM: ADDRESS OPCODE LABEL MNEMONICS OPERAND COMMENT 4100 MOV DPTR, #4200 4103 MOVX A, @DPTR 4104 MOV R0, A 4105 MOV B, #00 4108 MOV R1, B 410A ADD CLR C C3 410B INC DPTR A3 410C MOVX A, @DPTR 410D ADD A, B 410F MOV B, A 4111 JNC NC 4113 INC R1 4114 NC INC DPTR 4116 MOV DPTR, #4500 4119 MOV A, R1 411A MOVX @DPTR, A 411B INC DPTR 411C MOV A, B 411E MOVX @DPTR, A 411F SJMP HLT

- 82. freshupdates.in 79 OBSERVATION: INPUT OUTPUT 4200 4500 4201 4202 45014203 RESULT: The sum of elements in an array is calculated.

- 83. freshupdates.in 80 7(b) 8051 - SUM USING STACK AIM: To find the sum of elements in an array using stack. ALGORITHM: 1. Start 2. Move the data to stack pointer 3. Move the data to accumulator 4. Move the data to reg B 5. Move the data to DPL 6. Push the value of A to stack 7. Push the value of B to stack 8. Push the value of DPL to stack 9. Halt

- 84. freshupdates.in 81 PROGRAM: ADDRESS OPCODE LABEL MNEMONICS OPERAND COMMENT 4100 MOV SP, #67 67 4103 MOV A, #88 88 4105 MOV B, #66 66 4108 MOV DPL, #43 43 410B PUSH A 410D PUSH B 410F PUSH DPL 4111 SJMP RESULT: The sum of elements in an array is calculated.

- 85. freshupdates.in 82 7(c) 8051 - SUM USING CALL OPTION AIM: To find the sum of elements in an array using call option. ALGORITHM: 1. Start 2. Move the data to DPTR 3. Move the data to accumulator 4. Adjacent call 4200 5. Add A & R0 6. Move the 16 bit data from A to DPTR 7. Move the data to accumulator 8. Move the data to R0 9. Return to 4107

- 86. freshupdates.in 83 PROGRAM: ADDRESS OPC ODE LABEL MNEMONICS OPERAND COMMENT 4100 MOV DPTR,# 4300 43,00 4103 MOV A, # 00 00 4105 ACALL 4200 42,00 4108 ADD A, R0 410B MOVX @DPTR,A 80 410D SJMP 410F MOVA,#02 02 4111 MOV R0, #01 01 RET OBSERVATION: INPUT OUTPUT 4200 4300 4202 RESULT: The sum of elements in an array using call option is calculated is calculated.

- 87. freshupdates.in 84 Ex.No:8 8(a) STEPPER MOTOR INTERFACING WITH 8051 AIM: To interface a stepper motor with 8051 microcontroller and operate it. THEORY: A motor in which the rotor is able to assume only discrete stationary angular position is a stepper motor. The rotary motion occurs in a step-wise manner from one equilibrium position to the next. Stepper Motors are used very wisely in position control systems like printers, disk drives, process control machine tools, etc. The basic two-phase stepper motor consists of two pairs of stator poles. Each of the four poles has its own winding. The excitation of any one winding generates a North Pole. A South Pole gets induced at the diametrically opposite side. The rotor magnetic system has two end faces. It is a permanent magnet with one face as South Pole and the other as North Pole. The Stepper Motor windings A1, A2, B1, B2 are cyclically excited with a DC current to run the motor in clockwise direction. By reversing the phase sequence as A1, B2, A2, B1, anticlockwise stepping can be obtained. 2-PHASE SWITCHING SCHEME: In this scheme, any two adjacent stator windings are energized. The switching scheme is shown in the table given below. This scheme produces more torque. ANTICLOCKWISE CLOCKWISE STEP A1 A2 B1 B2 DATA STEP A1 A2 B1 B2 DATA 1 1 0 0 1 9h 1 1 0 1 0 Ah 2 0 1 0 1 5h 2 0 1 1 0 6h 3 0 1 1 0 6h 3 0 1 0 1 5h 4 1 0 1 0 Ah 4 1 0 0 1 9h ADDRESS DECODING LOGIC: The 74138 chip is used for generating the address decoding logic to generate the device select pulses, CS1 & CS2 for selecting the IC 74175.The 74175 latches the data bus to the stepper motor driving circuitry. Stepper Motor requires logic signals of relatively high power. Therefore, the interface circuitry that generates the driving pulses use silicon darlington pair transistors. The inputs for the interface circuit are TTL pulses generated under software control using the Microcontroller Kit. The TTL levels of pulse sequence from the data bus is translated to high voltage output pulses using a buffer 7407 with open collector.

- 88. freshupdates.in 85 BLOCK DIAGRAM: REPRESENTATION: 8051 MICROCONTROLLER 8255 DRIVER CIRCUIT STEPPER MOTOR

- 89. freshupdates.in 86 PROGRAM : Address OPCODES Label MNEM ONICS OPERAND Comments ORG 4100h 4100 START MOV DPTR, #TABLE Load the start address of switching scheme data TABLE into Data Pointer (DPTR) 4103 MOV R0, #04 Load the count in R0 4105 LOOP: MOVX A, @DPTR Load the number in TABLE into A 4106 PUSH DPH Push DPTR value to Stack4108 PUSH DPL 410A MOV DPTR, #0FFC0h Load the Motor port address into DPTR 410D MOVX @DPTR, A Send the value in A to stepper Motor port address 410E MOV R4, #0FFh Delay loop to cause a specific amount of time delay before next data item is sent to the Motor 4110 DELA Y: MOV R5, #0FFh 4112 DELA Y1: DJNZ R5, DELAY1 4114 DJNZ R4, DELAY 4116 POP DPL POP back DPTR value from Stack4118 POP DPH 411A INC DPTR Increment DPTR to point to next item in the table 411B DJNZ R0, LOOP Decrement R0, if not zero repeat the loop 411D SJMP START Short jump to Start of the program to make the motor rotate continuously 411F TABLE : DB 09 05 06 0Ah Values as per two- phase switching scheme

- 90. freshupdates.in 87 PROCEDURE: 1. Enter the above program starting from location 4100.and execute the same. 2. The stepper motor rotates. 3. Varying the count at R4 and R5 can vary the speed. 4. Entering the data in the look-up TABLE in the reverse order can vary direction of rotation. RESULT: Thus a stepper motor was interfaced with 8051 and run in forward and reverse directions at various speeds.

- 91. freshupdates.in 88 8 (b) INTERFACING D/A CONVERTER WITH 8051 AIM: To interface DAC with 8051 to demonstrate the generation of square, saw tooth and triangular wave. APPARATUS REQUIRED: SL.NO ITEM SPECIFICATION QUANTITY 1 Microprocessor kit 4185,Vi Microsystems 1 2 Power supply +5 V dc 1 3 DAC Interface board Vi Microsystems 1 THEORY: SOFTWARE EXAMPLES After going through the software examples you can learn how to control the DAC using 8051 and generate sine wave, saw tooth wave etc by means of software. ALGORITHM: (a) SQUARE WAVE GENERATION: 1. Load the initial value (00) to Accumulator and move it to DAC. 2. Call the delay program 3. Load the final value (FF) to accumulator and move it to DAC. 4. Call the delay program. 5. Repeat steps 2 to 5.

- 93. freshupdates.in 90 OBSERVATION: WAVE FORMS AMPLITUDE TIME PERIOD Square waveform Saw tooth waveform Triangular waveform PROGRAM: The basic idea behind the generation of waveforms is the continuous generation of Analog output of DAC. With 00(HEX) as input to DAC2, the analog output is -5V. Similarly, with FF (Hex) as input, the output is +5V. Outputting digital data 00 and FF at regular intervals, to DAC2, results in a square wave of amplitude I5 Volts. ADDRESS LABEL MNEMON ICS OPCODE OPERAND COMMENT MOV DPTR,#FFC8 START MOV A,#00 MOVX @DPTR,A LCALL DELAY MOV A,# FF MOVX @DPTR,A LCALL DELAY LJMP START DELAY MOV R1,#05 LOO[P MOV R2,#FF DJNZ R2,HERE DJNZ R1,LOOP RET SJMP START Execute the program and using a CRO, verify that the waveform at the DAC2 output is a square-wave. Modify the frequency of the square-wave, by varying the time delay. (b) SAW TOOTH GENERATION 1. Load the initial value (00) to Accumulator 2. Move the accumulator content to DAC. 3. Increment the accumulator content by 1. 4. Repeat steps 3 and 4. Output digital data from 00 to FF constant steps of 01 to DAC1 repeat this sequence again and again. As a result a saw – tooth wave will be generated at DAC1 output.

- 94. freshupdates.in 91 PROGRAM: ADDRESS LABEL MNEMON ICS OPCODE OPERAND COMMENT MOV DPTR,#FFC0 MOV A,#00 LOOP MOVX @DPTR,A INC A SJMP LOOP (c) TRIANGULAR WAVE GENERATION 1. Load the initial value (00) to Accumulator. 2. Move the accumulator content to DAC 3. Increment the accumulator content by 1. 4. If accumulator content is zero proceed to next step. Else go to step 3. 5. Load value (FF) to accumulator. 6. Move the accumulator content to DAC. 7. Decrement the accumulator content by 1. 8. If accumulator content is zero go to step 2. Else go to step 2. The following program will generate a triangular wave at DAC2 output. The program is self explanatory. ADDRESS LABEL MNEMON ICS OPCODE OPERAND COMMENT MOV DPTR,#FFC8 START MOV A,#00 LOOP1 MOVX @DPTR,A INC A JNZ LOOP1 MOV A,#FF LOOP2 MOVX @DPTR,A DEC A JNZ LOOP2 LJMP START OBSERVATION: WAVE FORMS AMPLITUDE TIME PERIOD Square waveform Saw tooth waveform Triangular waveform

- 95. freshupdates.in 92 Result: Thus the square, triangular and saw tooth wave form were generated by interfacing DAC with 8051 trainer kit.

- 96. freshupdates.in 93 Ex. No: 9 STUDY OF BASIC DIGITAL ICS AIM: To verify the truth table of basic digital ICs of AND, OR, NOT, NAND, NOR, EX-OR gates. APPARATUS REQUIRED: S.No Name of the Apparatus Range Quantity 1. Digital IC trainer kit 1 2. AND gate IC 7408 1 3. OR gate IC 7432 1 4. NOT gate IC 7404 1 5. NAND gate IC 7400 1 6. NOR gate IC 7402 1 7. EX-OR gate IC 7486 1 8. Connecting wires As required THEORY: a. AND gate: An AND gate is the physical realization of logical multiplication operation. It is an electronic circuit which generates an output signal of ‘1’ only if all the input signals are ‘1’. b. OR gate: An OR gate is the physical realization of the logical addition operation. It is an electronic circuit which generates an output signal of ‘1’ if any of the input signal is ‘1’. c. NOT gate: A NOT gate is the physical realization of the complementation operation. It is an electronic circuit which generates an output signal which is the reverse of the input signal. A NOT gate is also known as an inverter because it inverts the input.

- 97. freshupdates.in 94 d. NAND gate: A NAND gate is a complemented AND gate. The output of the NAND gate will be ‘0’ if all the input signals are ‘1’ and will be ‘1’ if any one of the input signal is ‘0’. e. NOR gate: A NOR gate is a complemented OR gate. The output of the OR gate will be ‘1’ if all the inputs are ‘0’ and will be ‘0’ if any one of the input signal is ‘1’. f. EX-OR gate: An Ex-OR gate performs the following Boolean function, A B = ( A . B’ ) + ( A’ . B ) It is similar to OR gate but excludes the combination of both A and B being equal to one. The exclusive OR is a function that give an output signal ‘0’ when the two input signals are equal either ‘0’ or ‘1’. PROCEDURE: 1. Connections are given as per the circuit diagram 1. For all the ICs 7th pin is grounded and 14th pin is given +5 V supply. 2. Apply the inputs and verify the truth table for all gates. AND GATE LOGIC DIAGRAM:

- 98. freshupdates.in 95 PIN DIAGRAM OF IC 7408: CIRCUIT DIAGRAM: TRUTH TABLE: S.No INPUT OUTPUT A B Y = A . B 1. 0 0 0 2. 0 1 0 3. 1 0 0 4. 1 1 1 OR GATE LOGIC DIAGRAM:

- 99. freshupdates.in 96 PIN DIAGRAM OF IC 7432 : CIRCUIT DIAGRAM: TRUTH TABLE: S.No INPUT OUTPUT A B Y = A + B 1. 0 0 0 2. 0 1 1 3. 1 0 1 4. 1 1 1 NOT GATE LOGIC DIAGRAM:

- 100. freshupdates.in 97 PIN DIAGRAM OF IC 7404 : CIRCUIT DIAGRAM: TRUTH TABLE: S.No INPUT OUTPUT A Y = A’ 1. 0 1 2. 1 0 NAND GATE LOGIC DIAGRAM:

- 101. freshupdates.in 98 PIN DIAGRAM OF IC 7400 : CIRCUIT DIARAM: TRUTH TABLE: S.No INPUT OUTPUT A B Y = (A. B)’ 1. 0 0 1 2. 0 1 1 3. 1 0 1 4. 1 1 0

- 102. freshupdates.in 99 NOR GATE LOGIC DIAGRAM: PIN DIAGRAM OF IC 7402 : CIRCUIT DIAGRAM: TRUTH TABLE: S.No INPUT OUTPUT A B Y = (A + B)’ 1. 0 0 1 2. 0 1 0 3. 1 0 0 4. 1 1 0

- 103. freshupdates.in 100 EX-OR GATE LOGIC DIAGRAM PIN DIAGRAM OF IC 7486: CIRCUIT DIAGRAM: TRUTH TABLE: S.No INPUT OUTPUT A B Y = A B 1. 0 0 0 2. 0 1 1 3. 1 0 1 4. 1 1 0

- 104. freshupdates.in 101 RESULT: The truth tables of all the basic digital ICs were verified. .

- 105. freshupdates.in 102 EX.NO.10 DESIGN AND IMPLEMENTATION OF ADDER/SUBTRACTOR AIM: To design and construct half adder, full adder, half subtractor and full subtractor circuits and verify the truth table using logic gates. APPARATUS REQUIRED: S. No Name Specification Quantity 1. IC 7432, 7408, 7486, 7483 1 2. Digital IC Trainer Kit 1 3. Patch chords - THEORY: The most basic arithmetic operation is the addition of two binary digits. There are four possible elementary operations, namely, 0 + 0 = 0 0 + 1 = 1 1 + 0 = 1 1 + 1 = 102 The first three operations produce a sum of whose length is one digit, but when the last operation is performed the sum is two digits. The higher significant bit of this result is called a carry and lower significant bit is called the sum. HALF ADDER: A combinational circuit which performs the addition of two bits is called half adder. The input variables designate the augend and the addend bit, whereas the output variables produce the sum and carry bits. FULL ADDER: A combinational circuit which performs the arithmetic sum of three input bits is called full adder. The three input bits include two significant bits and a previous carry bit. A full adder circuit can be implemented with two half adders and one OR gate.

- 106. freshupdates.in 103 HALF ADDER TRUTH TABLE: S.No INPUT OUTPUT A B S C 1. 0 0 0 0 2. 0 1 1 0 3. 1 0 1 0 4. 1 1 0 1 DESIGN: From the truth table the expression for sum and carry bits of the output can be obtained as, Sum, S = A B ; Carry, C = A . B CIRCUIT DIAGRAM: FULL ADDER TRUTH TABLE: S.No INPUT OUTPUT A B C SUM CARRY 1. 0 0 0 0 0 2. 0 0 1 1 0 3. 0 1 0 1 0 4. 0 1 1 0 1 5. 1 0 0 1 0 6. 1 0 1 0 1 7. 1 1 0 0 1 8. 1 1 1 1 1

- 107. freshupdates.in 104 DESIGN: From the truth table the expression for sum and carry bits of the output can be obtained as,SUM = A’B’C + A’BC’ + AB’C’ + ABC;CARRY = A’BC + AB’C + ABC’ +ABC Using Karnaugh maps the reduced expression for the output bits can be obtained as, SUM SUM = A’B’C + A’BC’ + AB’C’ + ABC = A B C CARRY CARRY = AB + AC + BC CIRCUIT DIAGRAM:

- 108. freshupdates.in 105 HALF SUBTRACTOR: A combinational circuit which performs the subtraction of two bits is called half subtractor. The input variables designate the minuend and the subtrahend bit, whereas the output variables produce the difference and borrow bits. FULL SUBTRACTOR: A combinational circuit which performs the subtraction of three input bits is called full subtractor. The three input bits include two significant bits and a previous borrow bit. A full subtractor circuit can be implemented with two half subtractors and one OR gate. HALF SUBTRACTOR TRUTH TABLE: S.No INPUT OUTPUT A B DIFF BORR 1. 0 0 0 0 2. 0 1 1 1 3. 1 0 1 0 4. 1 1 0 0 DESIGN: From the truth table the expression for difference and borrow bits of the output can be obtained as, Difference, DIFF = A B; Borrow, BORR = A’ . B CIRCUIT DIAGRAM:

- 109. freshupdates.in 106 FULL SUBTRACTOR TRUTH TABLE: S.No INPUT OUTPUT A B C DIFF BORR 1. 0 0 0 0 0 2. 0 0 1 1 1 3. 0 1 0 1 1 4. 0 1 1 0 1 5. 1 0 0 1 0 6. 1 0 1 0 0 7. 1 1 0 0 0 8. 1 1 1 1 1 DESIGN: From the truth table the expression for difference and borrow bits of the output can be obtained as, Difference, DIFF= A’B’C + A’BC’ + AB’C’ + ABC Borrow, BORR = A’BC + AB’C + ABC’ +ABC Using Karnaugh maps the reduced expression for the output bits can be obtained as, DIFFERENCE DIFF = A’B’C + A’BC’ + AB’C’ + ABC = A B C BORROW BORR = A’B + A’C + BC

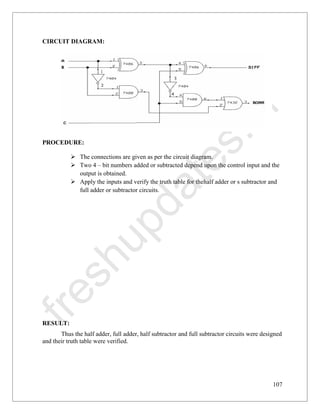

- 110. freshupdates.in 107 CIRCUIT DIAGRAM: PROCEDURE: The connections are given as per the circuit diagram. Two 4 – bit numbers added or subtracted depend upon the control input and the output is obtained. Apply the inputs and verify the truth table for thehalf adder or s subtractor and full adder or subtractor circuits. RESULT: Thus the half adder, full adder, half subtractor and full subtractor circuits were designed and their truth table were verified.

- 111. freshupdates.in 108 EX.NO.11 11(a) CODE CONVERTER AIM: To construct and verify the performance of binary to gray and gray to binary. APPARATUS REQUIRED: S. No Name Specification Quantity 1. IC 7404, 7486 1 2. Digital IC Trainer Kit 1 3. Patch chords - THEORY: BINARY TO GRAY: The MSB of the binary code alone remains unchanged in the Gray code. The remaining bits in the gray are obtained by EX-OR ing the corresponding gray code bit and previous bit in the binary code. The gray code is often used in digital systems because it has the advantage that only one bit in the numerical representation changes between successive numbers. GRAY TO BINARY: The MSB of the Gray code remains unchanged in the binary code the remaining bits are obtained by EX – OR ing the corresponding gray code bit and the previous output binary bit. PROCEDURE: Connections are given as per the logic diagram. The given truth tables are verified.

- 112. freshupdates.in 109 BINARY TO GRAY: GRAY TO BINARY

- 113. freshupdates.in 110 TRUTH TABLE Decimal Binary code Gray code D C B A G3 G2 G1 GO 0 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 1 2 0 0 1 0 0 0 1 1 3 0 0 1 1 0 0 1 0 4 0 1 0 0 0 1 1 0 5 0 1 0 1 0 1 1 1 6 0 1 1 0 0 1 0 1 7 0 1 1 1 0 1 0 0 8 1 0 0 0 1 1 0 0 9 1 0 0 1 1 1 0 1 10 1 0 1 0 1 1 1 1 11 1 0 1 1 1 1 1 0 12 1 1 0 0 1 0 1 0 13 1 1 0 1 1 0 1 1 14 1 1 1 0 1 0 0 1 15 1 1 1 1 1 0 0 0 RESULT: The design of the three bit Binary to Gray code converter & Gray to Binary code converter circuits was done and its truth table was verified.

- 114. freshupdates.in 111 11(b) ENCODER AIM: To design and implement encoder using IC 74148 (8-3 encoder) APPARATUS REQUIRED: S. No Name Specification Quantity 1. IC 74148 1 2. Digital IC Trainer Kit 1 3. Patch chords - THEORY: An encoder is digital circuit that has 2n input lines and n output lines. The output lines generate a binary code corresponding to the input values 8 – 3 encoder circuit has 8 inputs, one for each of the octal digits and three outputs that generate the corresponding binary number. Enable inputs E1 should be connected to ground and Eo should be connected to VCC PROCEDURE: Connections are given as per the logic diagram. The truth table is verified by varying the inputs. PIN DIAGRAM OUTPUT 2N INPUT NENCODER 1 2 1 2 N2N-1 2N

- 115. freshupdates.in 112 TRUTH TABLE E1 INPUTS OUTPUTS A0 A1 A2 A3 A4 A5 A6 A7 D2 D1 D0 0 0 1 1 1 1 1 1 1 0 0 0 0 1 0 1 1 1 1 1 1 0 0 1 0 1 1 0 1 1 1 1 1 0 1 0 0 1 1 1 0 1 1 1 1 0 1 1 0 1 1 1 1 0 1 1 1 1 0 0 0 1 1 1 1 1 0 1 1 1 0 1 0 1 1 1 1 1 1 0 1 1 1 0 0 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

- 116. freshupdates.in 113 11(c) DECODER AIM: To design and implement decoder using IC 74155 (3-8 decoder). APPARATUS REQUIRED: S. No Name Specification Quantity 1. IC 74155 1 2. Digital IC Trainer Kit 1 3. Patch chords - THEORY: A decoder is a combinational circuit that converts binary information from n input lines to 2n unique output lines. In 3-8 line decoder the three inputs are decoded into right outputs in which each output representing one of the minterm of 3 input variables. IC 74155 can be connected as a dual 2*4 decoder or a single 3*8 decoder desired input in C1 and C2 must be connected together and used as the C input. G1 and G2 should be connected and used as the G (enable) input. G is the enable input and must be equal to 0 for proper operation. PROCEDURE: Connections are given as per the logic diagram. The truth table is verified by varying the inputs. CIRCUIT DIAGRAM: OUTPUTN 1 2 1 2 N N INPUT DECODER 2N 2N-1

- 117. freshupdates.in 114 TRUTH TABLE INPUTS OUTPUTS G C B A 2Y0 2Y1 2Y2 2Y3 1Y0 1Y1 1Y2 1Y3 1 X X X 1 1 1 1 1 1 1 1 0 0 0 0 0 1 1 1 1 1 1 1 0 0 0 1 1 0 1 1 1 1 1 1 0 0 1 0 1 1 0 1 1 1 1 1 0 0 1 1 1 1 1 0 1 1 1 1 0 1 0 0 1 1 1 1 0 1 1 1 0 1 0 1 1 1 1 1 1 0 1 1 0 1 1 0 1 1 1 1 1 1 0 1 0 1 1 1 1 1 1 1 1 1 1 0 RESULT: Thus the encoder and decoder circuits were designed and implemented.

- 118. freshupdates.in 115 EX.NO.12 STUDY OF FLIP FLOPS AIM: To verify the characteristic table of RS, D, JK, and T Flip flops . APPARATUS REQUIRED: S.No Name of the Apparatus Range Quantity 1. Digital IC trainer kit 1 2. NOR gate IC 7402 3. NOT gate IC 7404 4. AND gate ( three input ) IC 7411 5. NAND gate IC 7400 6. Connecting wires As required THEORY: A Flip Flop is a sequential device that samples its input signals and changes its output states only at times determined by clocking signal. Flip Flops may vary in the number of inputs they possess and the manner in which the inputs affect the binary states. RS FLIP FLOP: The clocked RS flip flop consists of NAND gates and the output changes its state with respect to the input on application of clock pulse. When the clock pulse is high the S and R inputs reach the second level NAND gates in their complementary form. The Flip Flop is reset when the R input high and S input is low. The Flip Flop is set when the S input is high and R input is low. When both the inputs are high the output is in an indeterminate state. D FLIP FLOP: To eliminate the undesirable condition of indeterminate state in the SR Flip Flop when both inputs are high at the same time, in the D Flip Flop the inputs are never made equal at the same time. This is obtained by making the two inputs complement of each other. JK FLIP FLOP: The indeterminate state in the SR Flip-Flop is defined in the JK Flip Flop. JK inputs behave like S and R inputs to set and reset the Flip Flop. The output Q is ANDed with K input and the clock pulse, similarly the output Q’ is ANDed with J input and the Clock pulse. When the clock pulse is zero both the AND gates are disabled and the Q and Q’ output retain their previous values. When the clock pulse is high, the J and K inputs reach the NOR gates. When both the inputs are high the output toggles continuously. This is called Race around condition and this must be avoided. T FLIP FLOP:

- 119. freshupdates.in 116 This is a modification of JK Flip Flop, obtained by connecting both inputs J and K inputs together. T Flip Flop is also called Toggle Flip Flop. RS FLIP FLOP LOGIC SYMBOL: CIRCUIT DIAGRAM: CHARACTERISTIC TABLE: CLOCK PULSE INPUT PRESENT STATE (Q) NEXT STATE(Q+1) STATUS S R 1 0 0 0 0 2 0 0 1 1 3 0 1 0 0 4 0 1 1 0 5 1 0 0 1 6 1 0 1 1 7 1 1 0 X 8 1 1 1 X D FLIP FLOP

- 120. freshupdates.in 117 LOGIC SYMBOL: CIRCUIT DIAGRAM: CHARACTERISTIC TABLE: CLOCK PULSE INPUT D PRESENT STATE (Q) NEXT STATE(Q+1) STATUS 1 0 0 0 2 0 1 0 3 1 0 1 4 1 1 1

- 121. freshupdates.in 118 JK FLIP FLOP LOGIC SYMBOL: CIRCUIT DIAGRAM: CHARACTERISTIC TABLE: CLOCK PULSE INPUT PRESENT STATE (Q) NEXT STATE(Q+1) STATUS J K 1 0 0 0 0 2 0 0 1 1 3 0 1 0 0 4 0 1 1 0 5 1 0 0 1 6 1 0 1 1 7 1 1 0 1 8 1 1 1 0

- 122. freshupdates.in 119 T FLIP FLOP LOGIC SYMBOL: CIRCUIT DIAGRAM: CHARACTERISTIC TABLE: CLOCK PULSE INPUT T PRESENT STATE (Q) NEXT STATE(Q+1) STATUS 1 0 0 0 2 0 1 0 3 1 0 1 4 1 1 0

- 123. freshupdates.in 120 PROCEDURE: 1. Connections are given as per the circuit diagrams. 2. For all the ICs 7th pin is grounded and 14th pin is given +5 V supply. 3. Apply the inputs and observe the status of all the flip flops. RESULT: The Characteristic tables of RS, D, JK, T flip flops were verified.

- 124. freshupdates.in 121 EX.NO.13 13(a)ASYNCHRONOUS COUNTER AIM: To implement and verify the truth table of an asynchronous decade counter. APPARATUS REQUIRED: S.No Name of the Apparatus Range Quantity 1. Digital IC trainer kit 1 2. JK Flip Flop IC 7473 2 4. NAND gate IC 7400 1 5. Connecting wires As required THEORY: Asynchronous decade counter is also called as ripple counter. In a ripple counter the flip flop output transition serves as a source for triggering other flip flops. In other words the clock pulse inputs of all the flip flops are triggered not by the incoming pulses but rather by the transition that occurs in other flip flops. The term asynchronous refers to the events that do not occur at the same time. With respect to the counter operation, asynchronous means that the flip flop within the counter are not made to change states at exactly the same time, they do not because the clock pulses are not connected directly to the clock input of each flip flop in the counter. PIN DIAGRAM OF IC 7473:

- 125. freshupdates.in 122 CIRCUIT DIAGRAM: TRUTH TABLE: S.No CLOCK PULSE OUTPUT D(MSB) C B A(LSB) 1 - 0 0 0 0 2 1 0 0 0 1 3 2 0 0 1 0 4 3 0 0 1 1 5 4 0 1 0 0 6 5 0 1 0 1 7 6 0 1 1 0 8 7 0 1 1 1 9 8 1 0 0 0 10 9 1 0 1 0 11 10 0 0 0 0 PROCEDURE: 1. Connections are given as per the circuit diagrams. 2. Apply the input and verify the truth table of the counter.

- 126. freshupdates.in 123 RESULT: The truth table of the Asynchronous counter was hence verified.

- 127. freshupdates.in 124 EX.NO.13 13(b) SHIFT REGISTERS AIM: To implement the following shift register using flip flop (i) SIPO (ii) SISO (iii) PISO (iv) PIPO APPARATUS REQUIRED: S. No Name Specification Quantity 1. IC 7474 1 2. Digital IC Trainer Kit 1 3. Patch chords - THEORY: A register is used to move digital data. A shift register is a memory in which information is shifted from one position in to another position at a line when one clock pulse is applied. The data can be shifted either left or right direction towards right or towards left. A shift register can be used in four ways depending upon the input in which the data are entered in to and takes out of it. The four configuration are given as Serial input – Serial output Parallel input – Serial output Serial input – Parallel output Parallel input – Parallel output RS or JK flip flop are used to construct shift register have D flip flop is used for constructing shift register. PROCEDURE: Give the connections as per the circuit Set or Reset at the pin 2 which it’s the MSB of serial data. Apply a single clock Set or Reset second digital input at pin 2. Repeat step 2 until all 4-bit data are taken away.

- 128. freshupdates.in 125 SHIFT REGISTER: IC 7474 CLR1 D1 CLK PR1 Q1 Q1 GND +5VCC CLKD2CLR2 PR2 Q2 Q2 _ _ 1 2 3 4 5 6 7 891011121314 SIPO LEFT SHIFT IC 7474 IC 7474 IC 7474IC 7474 Q3 Q2 Q1 Q0 +5VCC D IN CLK +5VCC 1 2 3 4 5 1 2 3 4 5 9 10 11 13 12 9 10 11 12 13 SIPO RIGHT SHIFT

- 129. freshupdates.in 126 SISO IC 7474 IC 7474 IC 7474IC 7474 +5VCC DIN CLK +5VCC 1 2 3 4 5 1 2 3 4 5 9 10 11 13 12 9 10 11 12 13 DOUT PIPO SISO Data input = 1100 Clock Serial input Serial output 0 0 0 4 1 1 8 1 1 12 0 0 16 0 0 Q2 Q1 Q0 D Q2 C B A

- 130. freshupdates.in 127 PIPO Clock Parallel input Parallel output A B C D QA QB QC QD 0 0 0 0 0 0 0 0 0 1 1 1 0 1 1 1 0 1 SIPO Left shift No of clk pulse Serial input Din Parallel output Q3 Q2 Q1 Q0 0 0 0 0 0 0 1 1 0 0 0 1 2 1 0 0 1 1 3 0 0 1 1 0 4 1 1 1 0 1 5 0 1 0 1 0 6 0 0 1 0 0 7 0 1 0 0 0 8 0 0 0 0 0 Right Shift No of clock pulse Serial input Din Parallel output Q3 Q2 Q1 Q0 0 0 0 0 0 0 1 1 1 0 0 0 2 1 0 1 0 0 3 0 1 0 1 0 4 1 1 1 0 1 5 0 0 1 1 0 6 0 0 0 1 1 7 0 0 0 0 1 8 0 0 0 0 0

- 131. freshupdates.in 128 RESULT: Thus the SISO, SIPO, PISO, PIPO shift registers were designed and implemented.

- 132. freshupdates.in 129 EX.NO.14 14(a) DIFFERENTIATOR AIM: To design a Differentiator circuit for the given specifications using Op-Amp IC 741. APPARATUS REQUIRED: S.No Name of the Apparatus Range Quantity 1. Function Generator 3 MHz 1 2. CRO 30 MHz 1 3. Dual RPS 0 – 30 V 1 4. Op-Amp IC 741 1 5. Bread Board 1 6. Resistors 7. Capacitors 8. Connecting wires and probes As required THEORY: The differentiator circuit performs the mathematical operation of differentiation; that is, the output waveform is the derivative of the input waveform. The differentiator may be constructed from a basic inverting amplifier if an input resistor R1 is replaced by a capacitor C1. The expression for the output voltage is given as, Vo = - Rf C1 (dVi /dt) Here the negative sign indicates that the output voltage is 180 0 out of phase with the input signal. A resistor Rcomp = Rf is normally connected to the non-inverting input terminal of the op-amp to compensate for the input bias current. A workable differentiator can be designed by implementing the following steps: 1. Select fa equal to the highest frequency of the input signal to be differentiated. Then, assuming a value of C1 < 1 µF, calculate the value of Rf. 2. Choose fb = 20 fa and calculate the values of R1 and Cf so that R1C1 = Rf Cf. 3. The differentiator is most commonly used in waveshaping circuits to detect high frequency components in an input signal and also as a rate–of–change detector in FM modulators. PIN DIAGRAM:

- 133. freshupdates.in 130 CIRCUIT DIAGRAM OF DIFFERENTIATOR: DESIGN: Given fa = --------------- We know the frequency at which the gain is 0 dB, fa = 1 / (2π Rf C1) Let us assume C1 = 0.1 µF; then Rf = _________ Since fb = 20 fa, fb = --------------- We know that the gain limiting frequency fb = 1 / (2π R1 C1) Hence R1 = _________ Also since R1C1 = Rf Cf ; Cf = _________ PROCEDURE: 1. Connections are given as per the circuit diagram. 2. + Vcc and - Vcc supply is given to the power supply terminal of the Op-Amp IC. 3. By adjusting the amplitude and frequency knobs of the function generator, appropriate input voltage is applied to the inverting input terminal of the Op-Amp. 4. The output voltage is obtained in the CRO and the input and output voltage waveforms are plotted in a graph sheet.

- 134. freshupdates.in 131 OBSERVATIONS: Input - Sine wave S.No. Amplitude ( No. of div x Volts per div ) Time period ( No. of div x Time per div ) Input Output Input – Square wave S.No. Amplitude ( No. of div x Volts per div ) Time period ( No. of div x Time per div ) Input Output DIFFERENTIATOR: INPUT SIGNAL: OUTPUT SIGNAL: Time Period AmplitudeAmplitude Time Period

- 135. freshupdates.in 132 RESULT: The design of the Differentiator circuit was done and the input and output waveforms were obtained.

- 136. freshupdates.in 133 14(b) INTEGRATOR AIM: To design an Integrator circuit for the given specifications using Op-Amp IC 741. APPARATUS REQUIRED: S.No Name of the Apparatus Range Quantity 1. Function Generator 3 MHz 1 2. CRO 30 MHz 1 3. Dual RPS 0 – 30 V 1 4. Op-Amp IC 741 1 5. Bread Board 1 6. Resistors 7. Capacitors 8. Connecting wires and probes As required THEORY: A circuit in which the output voltage waveform is the integral of the input voltage waveform is the integrator. Such a circuit is obtained by using a basic inverting amplifier configuration if the feedback resistor Rf is replaced by a capacitor Cf . The expression for the output voltage is given as, Vo = - (1/Rf C1) ∫ Vi dt Here the negative sign indicates that the output voltage is 180 0 out of phase with the input signal. Normally between fa and fb the circuit acts as an integrator. Generally, the value of fa < fb . The input signal will be integrated properly if the Time period T of the signal is larger than or equal to Rf Cf. That is, T ≥ Rf Cf The integrator is most commonly used in analog computers and ADC and signal-wave shaping circuits. PIN DIAGRAM:

- 137. freshupdates.in 134 CIRCUIT DIAGRAM OF INTEGRATOR: DESIGN: We know the frequency at which the gain is 0 dB, fb = 1 / (2π R1 Cf) Therefore fb = _____ Since fb = 10 fa, and also the gain limiting frequency fa = 1 / (2π Rf Cf) We get, Rf = _______ and hence R1 = __________ PROCEDURE: 1. Connections are given as per the circuit diagram. 2. + Vcc and - Vcc supply is given to the power supply terminal of the Op-Amp IC. 3. By adjusting the amplitude and frequency knobs of the function generator, appropriate input voltage is applied to the inverting input terminal of the Op-Amp.

- 138. freshupdates.in 135 4. The output voltage is obtained in the CRO and the input and output voltage waveforms are plotted in a graph sheet. OBSERVATIONS: S.No. Amplitude ( No. of div x Volts per div ) Time period ( No. of div x Time per div ) Input Output MODEL GRAPH: INTEGRATOR: INPUT SIGNAL: OUTPUT SIGNAL: RESULT: The design of the Integrator circuit was done and the input and output waveforms were obtained. AmplitudeAmplitude Time Period

- 139. freshupdates.in 136 EX.NO. 15 15(a) TIMER IC APPLICATIONS - I (ASTABLE MULTIVIBRATOR) AIM: To design an astable multivibrator circuit for the given specifications using 555 Timer IC. APPARATUS REQUIRED: S. No Name of the Apparatus Range Quantity 1. Function Generator 3 MHz 1 2. CRO 30 MHz 1 3. Dual RPS 0 – 30 V 1 4. Timer IC IC 555 1 5. Bread Board 1 6. Resistors 7. Capacitors 8. Connecting wires and probes As required THEORY: An astable multivibrator, often called a free-running multivibrator, is a rectangular- wave-generating circuit. This circuit do not require an external trigger to change the state of the output. The time during which the output is either high or low is determined by two resistors and a capacitor, which are connected externally to the 555 timer. The time during which the capacitor charges from 1/3 Vcc to 2/3 Vcc is equal to the time the output is high and is given by, tc = 0.69 (R1 + R2) C Similarly the time during which the capacitor discharges from 2/3 Vcc to 1/3 Vcc is equal to the time the output is low and is given by, td = 0.69 (R2) C Thus the total time period of the output waveform is, T = tc + td = 0.69 (R1 + 2 R2) C The term duty cycle is often used in conjunction with the astable multivibrator. The duty cycle is the ratio of the time tc during which the output is high to the total time period T. It is generally expressed in percentage. In equation form, % duty cycle = [(R1 + R2) / (R1 + 2 R2)] x 100

- 140. freshupdates.in 137 PIN DIAGRAM: CIRCUIT DIAGRAM OF ASTABLE MULTIVIBRATOR:

- 141. freshupdates.in 138 DESIGN: Given f= 4 KHz, Therefore, Total time period, T = 1/f = ____________ We know, duty cycle = tc / T Therefore, tc = ------------------------ and td = ____________ We also know for an astable multivibrator td = 0.69 (R2) C Therefore, R2 = _____________ tc = 0.69 (R1 + R2) C Therefore, R1 = _____________ PROCEDURE: 1. Connections are given as per the circuit diagram. 2. + 5V supply is given to the + Vcc terminal of the timer IC. 3. At pin 3 the output waveform is observed with the help of a CRO 4. At pin 6 the capacitor voltage is obtained in the CRO and the V0 and Vc voltage waveforms are plotted in a graph sheet. OBSERVATIONS: S.No Waveforms Amplitude ( No. of div x Volts per div ) Time period ( No. of div x Time per div ) tc td 1. Output Voltage , Vo 2. Capacitor voltage , Vc

- 142. freshupdates.in 139 MODEL GRAPH: RESULT: The design of the Astable multivibrator circuit was done and the output voltage and capacitor voltage waveforms were obtained. O/p voltage T (ms) Capacitor voltage Vcc 2/3 Vcc 1/3 Vcc TON TOFF

- 143. freshupdates.in 140 15(b) TIMER IC APPLICATIONS –II (MONOSTABLE MULTIVIBRATOR) AIM: To design a monostable multivibrator for the given specifications using 555 Timer IC. APPARATUS REQUIRED: S.No Name of the Apparatus Range Quantity 1. Function Generator 3 MHz, Analog 1 2. CRO 30 MHz 1 3. Dual RPS 0 – 30 V 1 4. Timer IC IC 555 1 5. Bread Board 1 6. Resistors 7. Capacitors 8. Connecting wires and probes As required THEORY: A monostable multivibrator often called a one-shot multivibrator is a pulse generating circuit in which the duration of the pulse is determined by the RC network connected externally to the 555 timer. In a stable or stand-by state the output of the circuit is approximately zero or at logic low level. When an external trigger pulse is applied, the output is forced to go high (approx. Vcc). The time during which the output remains high is given by, tp = 1.1 R1 C At the end of the timing interval, the output automatically reverts back to its logic low state. The output stays low until a trigger pulse is applied again. Then the cycle repeats. Thus the monostable state has only one stable state hence the name monostable. PIN DIAGRAM:

- 144. freshupdates.in 141 CIRCUIT DIAGRAM OF MONOSTABLE MULTIVIBRATOR: DESIGN: Given tp = 0.616 ms = 1.1 R1 C Therefore, R1 = _____________ PROCEDURE: 1. Connections are given as per the circuit diagram. 2. + 5V supply is given to the + Vcc terminal of the timer IC. 3. A negative trigger pulse of 5V, 2 KHz is applied to pin 2 of the 555 IC 4. At pin 3 the output waveform is observed with the help of a CRO 5. At pin 6 the capacitor voltage is obtained in the CRO and the V0 and Vc voltage waveforms are plotted in a graph sheet. OBSERVATIONS: S.No Amplitude ( No. of div x Volts per div ) Time period ( No. of div x Time per div ) ton toff 1. Trigger input 2. Output Voltage , Vo 3. Capacitor voltage , Vc

- 145. freshupdates.in 142 MODEL GRAPH: RESULT: The design of the Monostable multivibrator circuit was done and the input and output waveforms were obtained.

![freshupdates.in

3

FLOW CHART:

NO

YES

START

[HL] 4500H

[A] [M]

[A] [A]+[M]

[HL] [HL]+1

STOP

[HL] [HL]+1

[M] [A]

[C] 00H

[M] [C]

[HL] [HL]+1

Is there a

Carry ?